### BAMBERGER BEITRÄGE ZUR WIRTSCHAFTSINFORMATIK UND ANGEWANDTEN INFORMATIK ISSN 0937-3349

### Nr. 102/Juli 2017

# Clock-Synchronised Shared Objects for Deterministic Concurrency

Joaquín Aguado, Michael Mendler, Marc Pouzet, Partha Roop, Reinhard von Hanxleden

Slightly Updated Version: February 2018 Second Update: April 2018

FAKULTÄT FÜR WIRTSCHAFTSINFORMATIK UND ANGEWANDTE INFORMATIK OTTO-FRIEDRICH-UNIVERSITÄT BAMBERG

## Clock-Synchronised Shared Objects for Deterministic Concurrency

(Update April 2018)\*

Joaquín Aguado<sup>1</sup>, Michael Mendler<sup>1</sup>, Marc Pouzet<sup>2</sup>, Partha Roop<sup>3</sup>, and Reinhard von Hanxleden<sup>4</sup>

Otto-Friedrich-Universität Bamberg, Germany

<sup>2</sup> École Normale Supérieure Paris, France

<sup>3</sup> University of Auckland, New Zealand

<sup>4</sup> Christian-Albrechts-Universität zu Kiel, Germany

Abstract. Traditional synchronous programming (SP) languages have been the paradigm of choice for the design of safety critical systems as they guarantee concurrent thread composition with observably deterministic behaviour, also called determinacy. However, this determinacy has a high price since the only means for communication between concurrent threads are shared signals. These only support simple built-in data types under restrictive read and write access protocols which prohibits modularity and behavioural abstractions. This contrast markedly with main stream programming which has long discovered abstract data types (ADTs) and the use of objects through which ADTs can be freely shared. In SP these are available only via host language support. While this achieves modularity, it sacrifices behavioural determinacy.

Can both developments be reconciled? This report combines the concept of *passive objects* with SP to propose *clock synchronised objects*. We use the main entry point of an object oriented (OO) program ("the main method") to create synchronous threads, which are allowed to make concurrent method invocations. Each object publishes a *policy interface* that defines the admissibility of and precedence between concurrent method accesses. Determinacy is then guaranteed for *policy-coherent* object implementations under *policy-conformant* method scheduling. A program is *policy-constructive* if it is deadlock-free. This yields a uniform approach for integrating existing SP languages within the same computational setting and extending them by an expressive component model that fills an abstraction gap still prevalent in standard SP languages.

Technically, we introduce a kernel language for clock synchronized shared objects, called *deterministic concurrent language* (DCoL). A reduction semantics for DCoL is developed for which we prove determinacy and

<sup>\*</sup> In this updated version we have fixed some typos and adjusted terminology to bring the text in line with the conference publication: J. Aguado, M. Mendler, M. Pouzet, P. Roop, R. von Hanxleden: Deterministic Concurrence: A Clocksynchronised Shared Memory Approach. In European Symposium on Programming (ESOP 2018), April 14-20, Thessaloniki 2018.

termination of constructive programs. We show that policy interfaces are generic enough to subsume existing SP such as Esterel signals, the recently proposed extension of sequentially constructive variables or more expressive frameworks such as Kahn data-flow channels. This opens the door to libraries of determinate shared objects encapsulating data and control.

#### 1 Introduction

Data race conditions pose significant problems for concurrent software [38]. These problems are aggravated with the rapid advances in multicore and many core architectures. A recent survey of debugging methods of concurrent software [6] over the past decade (2005-2014) observes: "...] developers, testers, debuggers and researchers still face interesting problems in data race issues. Since this bug is one of the most difficult bugs to reproduce researchers are still challenged by improving the available solutions." Considering this there is even a call for making parallel programming deterministic by construction [15]. While this is hard to achieve for general-purpose concurrent programming, there exist domain-specific concurrent languages which have made determinacy their hallmark from the outset. An example is the synchronous programming (SP) [7] paradigm. The most well-known SP languages with long history are Signal [32], Lustre [33] for data-flow or Esterel [12] for control-flow dominated systems or Esterel V7 [51] for combined models. More recent examples of SP languages are Lucid Synchrone [44] in data-flow style or Reactive ML [39], Quartz [48] or SC [53] in control-flow style.

Synchronous Programming: Step-by-Step Determinacy. The trick used by the synchronous model of computation (SMoC) is to reduce the programming of determinate concurrent systems to the programming of clock-synchronised communicating reaction modules that operate in lock-step. At each *clock tick*, also called *macro-step* or *(synchronous) instant*, each concurrent program module reads inputs from the environment and executes a step function to change internal memory and produce an output which is consumed by the environment during the same instant. The so-called *Synchrony Hypothesis* assumes that scheduling can be so arranged that the system's reaction is always faster than its environment. In this way, the externally observable behaviour can be abstracted as a synchronous Mealy automaton.

The presence of a global clock does not eliminate data races completely, however. Yet, it makes their effect remain contained within the temporal barriers of the clock. Within a macro step, all *micro-step* accesses to shared memory must be controlled by some other means. Here, traditional imperative SP languages play it safe by offering *signals* as only means for data exchange between concurrent threads. Signals behave like shared variables for which all read and write accesses occurring within a macro step are synchronised by a *default-combineread* protocol. It ensures that (1) at the beginning of each instant every signal is initialised to a default value, (2) within each instant writes are scheduled before the reads and (3) multiple writes to a (valued) signal are prevented unless the user provides a commutative and associative *combine function*.

Programs which cannot be scheduled in this way are considered *non-cons-tructive* [9] and rejected. As a consequence, all destructive updates of shared data must be separated by a clock tick and thus require global synchronisation. This is expensive in distributed implementations and makes data and control abstraction extremely difficult. For complex applications that involve abstract data types (ADTs), SP languages rely on a host language, such as C, to implement the required functionality. While explicit sharing of variables is prevented by SP compilers, hidden sharing and race conditions are possible through the host function calls. This determinacy leak is a risk for safety-critical applications and jeopardises the mathematical simplicity of the SMoC.

Synchronous Programming and Objects. Considering the importance of ADTs and the successes of the object-oriented (OO) paradigm in main-stream programming, it is natural to look for a better integration of object models within SP. Key benefits of the OO paradigm such as *information hiding, cohesion, coupling* and *separation of concerns* are as important for safety-critical applications as they are for main-stream software engineering. Could we leverage the elegance of OO for ADT support combined with synchronous reactivity for determinacy? This would require a generalisation of the concept of signals to that of clock-synchronised shared ADTs. How this can be done is not obvious.

Object encapsulation itself is not entirely unknown in reactive programming [18,42,5]. The idea of reactive object model (ROM) was first introduced by Boussinot et al. [18] and has been further refined in subsequent approaches [49] and also combined with OO standards such as UML [5]. Here a program is a collection of reactive objects that operate synchronously relative to a global clock, similar to SP. In spite of these advances in reactive objects, several central questions remain. Any combination of SP with OO must strive to achieve the best of both worlds, namely deterministic concurrency (from SP) combined with data abstraction (from OO). In ROM [18] determinacy is indeed addressed, yet it is achieved through maximally-conservative synchronisation, forcing each two method invocations to be separated by a clock tick. This heavy global synchronisation is expensive on a concurrent platform, often unnecessary and preventing behavioural abstractions. While synchronous objects [4] are less restrictive due to their reliance on Esterel-style signals for object synchronisation, they lack more general shared object models beyond restrictive signals. In particular, like all of the approaches on SP objects which we are aware of, they cannot handle destructive updates of shared memory within a macro step while preserving determinate behaviour.

**Contributions.** We propose a synchronous language with a notion of shared objects that permit intra-instant destructive updates. To reconcile concurrent sharing with determinacy, the shared objects have access policies associated with their method interface expressing *precedence* and *admissibility* constraints. By

restricting the scheduling of *concurrent* method calls within each synchronous clock instant, *policy conformance* eliminates all potential data races. This combines the clock mechanism from SP for determinacy with the OO mechanism for data abstraction. It exploits a natural trade-off between (i) the positioning of the clock barrier instructions (pause) with (ii) the tightness of object policies as restrictions on accesses not separated by the barrier. If an object behaves deterministically under a given policy we call it *policy-coherent*. If a program can be scheduled in a policy-conformant fashion without deadlock we call it *policy-constructive*. While coherence is determined by the available confluence of methods *inside* an object, constructiveness depends on the degree of concurrency of the environment *outside* the object. This is inspired by the policies of Caspi et al. [21] defined over *modes* for accessing shared *state variables*. A key contribution of this work is to reformulate the policies in [21] in the light of recent work on sequential constructiveness [56] so they can be used to generalise the semantics of SP signals to shared ADTs.

Our technical contributions are the following: We formally define the policy conformance for synchronous objects. We present the kernel deterministic concurrent language language DCoL and its generic fixed-point semantics to implement a constructive scheduling mechanism parametrised in arbitrary perobject precedence policies. DCoL is both a minimalistic kernel language to study the new mathematical concepts but can also act as an intermediate language for compiling existing SP. We define the semantics as a structurally inductive big-step reduction relation and call a program *policy-constructive* if the reduction is deadlock free. We prove that for policy-coherent objects, every policyconstructive program is determinate. This extends the well-known SP notion of constructiveness to general shared objects. In particular, it subsumes both the notions of Berry-constructiveness [9] for Esterel and sequential constructiveness for SCL [56]. This is the first time that these SP communication principles are combined side-by-side in a single language. Moreover, it permits other predefined communication structures to coexist safely under the same uniform principle, such as data-flow variables [33], registers [45], Kahn channels [34], priority queues, arrays as well as other ADTs implemented using OO libraries.

#### 2 A Clock-Synchronised Object Language (DCoL)

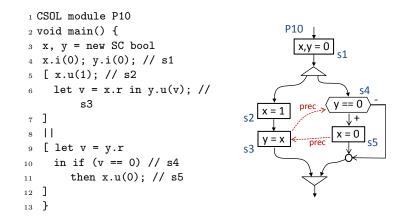

This work studies the semantical foundations of an imperative kernel language, called *deterministic concurrent language* (DCoL), to integrate policy-controlled shared objects within a simple programming syntax. It comprises the operators seen in Fig. 2.

The first two statements skip and pause are empty programs representing the two forms of immediate *completion*: skip terminates instantaneously, while pause waits for the logical clock and terminates in the next instant. The operators  $P \parallel Q$  and P;Q are *parallel interleaving* and *imperative sequential* composition of threads with the standard operational interpretation. Reading

| $P =_{df}$ | skip                                                                | instantaneous termination                         |

|------------|---------------------------------------------------------------------|---------------------------------------------------|

|            | pause                                                               | wait for next instant (clock tick)                |

|            | $P \parallel P$                                                     | parallel composition                              |

|            | P;P                                                                 | sequential composition                            |

| Í          | ${\tt if}e{\tt then}P{\tt else}P$                                   | conditional branching, $e$ value expression       |

|            | $\operatorname{let} x = \operatorname{c.} m(e) \operatorname{in} P$ | method call, $x$ statically scoped value variable |

|            | $\operatorname{rec} p. P$                                           | recursive closure                                 |

|            | p                                                                   | process variable                                  |

|            |                                                                     |                                                   |

Fig. 1. Syntax of DCoL

and destructive updating of shared memory is performed through the evaluation of an method call c.m(e) in a synchronised object  $c \in O$ . The set of *objects* O defines the granularity of the available memory accesses. The construct let x = c.m(e) in P calls method m of object  $c \in O$  with input parameter determined by a *value expression* e. It binds the return value to variable x and then executes program P, which may depend on x, sequentially afterwards. The execution of c.m(e) in general has the side-effect of changing the internal memory of c. In contrast, the evaluation of a value expression e is side-effect free.

It will be often more convenient to write let x = c.m(e) in P like an assignment prefix x = c.m(e); P ignoring that x is not a memory but a stack-allocated value variable. When P does not depend on the return value of the method call then we write  $let_{-} = c.m(e)$  in P or even c.m(e); P. The exact syntax of value expressions e is irrelevant for this work and left open. It could be as simple as permitting only constant value literals or a full-fledged functional programming language. Method calls without parameter are also written c.m instead of c.m().

The recursive closure  $\operatorname{rec} p. P$  binds the behaviour P to the program label p so it can be called from within the program P. Using this construct we can build iterative behaviours. For instance,  $\operatorname{halt} =_{df} \operatorname{rec} p. \operatorname{pause}; p$  is the program that synchronises with the clock indefinitely without any effect on the memory. We assume that recursions  $\operatorname{rec} p. P$  are (i) *clock guarded*, i.e., the label p is occurs in the scope of at least one pause and (ii) *thread-linear*, i.e., all occurrences of p are in the same thread. For instance,  $\operatorname{rec} p. p$  is illegal as it violates (i) and  $\operatorname{rec} p.$  (pause;  $p \parallel \operatorname{pause}; p)$  is not permitted since it violates (ii).

An expression P closed if it does not contain any free process or value variables, i.e., any process variable p must appear in the scope of a recursion rec p. P and each value variable in the scope of a method call let x = c.m(e). We will assume throughout that programs are closed, clock-guarded and thread-linear.

Our syntax is somewhat minimalistic compared to existing full-fledged synchronous programming languages. For instance, it does not provide control-flow primitives for preemption, suspension or traps like in Quartz or Esterel. However, these are not essential for an intermediate language. Recent work [46] has shown how these these higher control primitives can be translated into the constructs of the language SCL exploiting destructive update of sequentially constructive (SC) variables. Since these are a special case of policy-synchronised objects, our kernel language is at least as expressive as SCL. Hence, in particular, both Quartz and Esterel can be compiled into DCoL.

#### 3 Motivation and Examples

The restrictive semantics of traditional SP languages precludes object-oriented component models, as they are now common in main-stream imperative programming. In this section we first discuss the problem and then present two extended examples to illustrate our new approach. Readers interested in the mathematical semantics may skip this section and directly continue with Sec. 4.

The most complex memory structure that can be shared through signals are arrays, e.g., in Lustre [47,40] or in the latest version Esterel V7 [11,51]. However, what about sharing lists, queues and other more abstract behavioural structures such as a user interface window? Defining such structures as objects, encapsulating their behaviour inside methods and sharing them between threads creates powerful abstraction mechanisms for concurrent object-oriented programming. Of course, the flexibility depends on the programmer's skills for safe synchronisation of object accesses through low-level primitives such as semaphores, locks or monitors. The strength of SP, in contrast, is to relieve the programmer from this burden and make the compiler guarantee clock determinate and dead-lock free scheduling. To do so, SP forces the programmer to express all shared interaction entirely through signals governed by the default-combine-read protocol. As a consequence, all destructive updates must be separated by a clock tick and thus require global synchronisation.<sup>5</sup> This makes data and control abstraction impossible for concurrent objects.

The pertinent limitation of SP languages is that they do not permit the programmer to prescribe imperative sequential control flow within an instant. There is no construct to express sequential execution order for destructive updates of signals as shared objects. All such updates are considered concurrent and thus must either be merged through a *combination function* or concern distinct signals. For instance, in languages such as Esterel V7 or Quartz, a parallel composition<sup>6</sup>

$$(v = x.read; y. emit(v + 1)) \parallel (x. emit(1); x. emit(5))$$

of signal *emissions* is only constructive if a commutative and associative function is defined on the shared signal  $\mathbf{x}$  to combine the values assigned to it. But then we get the same behaviour if we swap the assignments of values 1 and 5, as in

$$(v = x.read; y. emit(v + 1)) \parallel (x. emit(5); x. emit(1))$$

<sup>&</sup>lt;sup>5</sup> SP languages do support normal reference variables which may have complex data types. These can be freely accessed from a single thread yet cannot be shared between threads.

<sup>&</sup>lt;sup>6</sup> In Esterel syntax this program is written  $\mathbf{y} \leftarrow \mathbf{x} + 1 \parallel (\mathbf{x} \leftarrow 1; \mathbf{x} \leftarrow 5)$ .

or execute them in parallel as in

$$(v = x.read; y.emit(v + 1)) \parallel x.emit(1) \parallel x.emit(5)$$

What if we want the second emission  $\mathbf{x}.\mathtt{emit}(5)$  to override the first  $\mathbf{x}.\mathtt{emit}(1)$  like in normal imperative programming and have the concurrent reading  $v = \mathbf{x}.\mathtt{read}; \mathbf{y}.\mathtt{emit}(v+1)$  see this updated value v = 5? Then, we must introduce a pause statement to separate the emissions by a clock tick and delay the assignment to  $\mathbf{y}$  as in

(pause;  $(v = x.read; y.emit(v + 1)) \parallel (x.emit(1); pause; x.emit(5)).$

Consequently, the default initialisation of a signal within an instant is not expressible inside the language itself. In normal imperative code we could write  $\mathbf{x} = def$ ; *P* to make def a default value for a signal  $\mathbf{x}$  in case program *P* does not write  $\mathbf{x}$ . In SP this does not work since any writing of  $\mathbf{x}$  by *P* gets combined with the default value def rather than destructively overwrite it.<sup>7</sup>

More seriously, the simple SP protocol prevents behavioural abstraction. For instance, suppose **nats** is a synchronous reaction module, possibly composite with its own internal clocking, which returns the stream of natural numbers. Every time its step function **nats.step** is called it returns the next number and increments its internal state. If we want to pair up two successive numbers within one instant of an outer clock and output them in a single signal y we would write something like  $x_1 = \text{nats.step}; x_2 = \text{nats.step}; y. \text{emit}(x_1, x_2)$  where  $x_1, x_2$  are thread-local value variables. This over-clocking is impossible in traditional SP because there is no imperative sequential composition by virtue of which we can call the step function of the same module instance twice within an instant. Instead, the two calls **nats.step** are considered concurrent and thus create nondeterminacy in the value of y.<sup>8</sup> To avoid a compiler error we must separate the calls by a clock as in  $x_1 = \text{nats.step}; pause; x_2 = \text{nats.step}; y. \text{emit}(x_1, x_2)$ which breaks the intended clock abstraction.

As another natural example of a behavioural abstraction suppose **x** is a signal whose values are pairs and we want to set the first component of **x** to *e* leaving the second unchanged. Assume  $\pi_1$  and  $\pi_2$  are the projections functions on pairs. In imperative code the access to the first element of **x** would be achieved by  $\mathbf{x} = (e, \pi_2 \mathbf{x})$  or  $y = \pi_2 \mathbf{x}; \mathbf{x} = (e, y)$  if we need to split off the reading of **x** into a separate statement from the emission to **x**. However, in SP this is non-constructive since the value of a signal **x** cannot be read before it is written.

<sup>&</sup>lt;sup>7</sup> The exception is if the default value happens to be the neutral element of the combination function. This is not normally the case when the default value is the signal's value from the previous instant or an environment input.

<sup>&</sup>lt;sup>8</sup> In Esterel V7 it is possible to use a module twice in a (non-imperative) sequential composition  $x_1 = \text{nats.step}$ ;  $x_2 = \text{nats.step}$ . However, then the two occurrences of nats are two distinct instances of the module with their own internal state. Both calls will thus return the same value. Calling modules by value (rather than reference) is a way of solving the non-determinacy problem but not for achieving object-orientation.

Again, we would need to break the update through a clock tick. In Esterel we would write<sup>9</sup>

$$v = x.read; pause; x.emit(e, \pi_2 v)$$

or  $v = x.pre; x.emit(e, \pi_2 v)$  where x.pre refers to the value of x from the previous instant.

Hence, if we were to use signals to represent general shared objects (of complex type) every method call " $\mathbf{x}.m(e)$ " would thus have to be broken by a clock tick either like in  $v = \mathbf{x}.pre; \mathbf{x}.emit(set_m(v, e))$  where the function  $set_m$  determines the new state by which  $\mathbf{x}$  is destructively updated, or as

```

v = x.read; pause; x.emit(set_m(v, e))

```

using a value variable v that stores the previous state of the object.

If we want more than one method call on the same object within a single instant we must program explicit combination functions for the object type.<sup>10</sup> However, this not only precludes destructive updates, like in the *def* value or the **nats** examples above. Worse, the programmer cannot exploit method calls that are computationally independent, without being forced to enrich the data types by extraneous dependency information. For instance, suppose again the object behind signal **x** is a pair  $(x_1, x_2) = \mathbf{x}$ .read and methods  $m_i$  act on the two components separately, say  $set_{m_1}((x_1, x_2), e) = (e, x_2)$  and  $set_{m_2}((x_1, x_2), e) = (x_1, e)$ . Then, without fiddling with the signal data type, the only way to implement an emission **x**. emit $(e_1, e_2)$  by parallel composition is

$$v = x.pre; (x.emit(set_{m_1}(v, e_1)) \parallel x.emit(set_{m_2}(v, e_2))).$$

Unfortunately, there is no commutative combination function  $f_c$  on pairs of values that could merge the two method calls to produce:

$$f_c(set_{m_1}((x_1, x_2), e_1), set_{m_2}((x_1, x_2), e_2)) = f_c((e_1, x_2), (x_1, e_2)) = (e_1, e_2)$$

for arbitrary  $x_i$  and  $e_i$ . The problem is that the function  $f_c$  cannot tell from the value pairs  $(e_1, x_2)$ ,  $(x_1, e_2)$  which of the components, in each case, is the old and which is the updated value. There is no such information in the data. The programmer is forced either to enrich the pair type by additional "indexing flags" or to use two distinct signals and write  $x_1.emit(e_1) \parallel x_2.emit(e_2)$  for which no combination function is needed.

To sum up, generally speaking, the data abstraction problem of the traditional SMoC is that there is little programming language support to package up a complex structure of synchronised signals as a synchronised signal of complex data. A *fortiori*, it is not possible to abstract synchronous behaviour into signal objects and share them between concurrent threads. Having observed that, let

<sup>&</sup>lt;sup>9</sup> The full syntax in DCoL would be let v = x.read in pause ; x. emit $(e, \pi_2 v)$

<sup>&</sup>lt;sup>10</sup> In the Esterel V7 standard proposal [51] combination functions on arrays can be defined but only on the primitive cells.

us stress that this limitation is not an artefact of language design. It is a natural consequence of the conservative view of program constructiveness according to which the synchronous clock is the only means to guarantee sequential ordering and atomic execution of accesses to (shared) signals in a concurrent execution environment. While this may be adequate for physical circuits and massively parallel hardware, this is an overly pessimistic stand for sequential execution platforms. It is well known how to use the *physical* clocks of the instruction set architecture to implement sequential destructive updates and atomic execution of memory accesses within a single *logical* clock instant of the synchronous programming abstraction. In this work we exploit this to generalise the signal concept of traditonal SP to arbitrary complex data structures. In the following two Secs. 3.1 and 3.2 we are going to illustrate our proposal by way of elaborated examples.

#### 3.1 Stop Watch – Extended Example

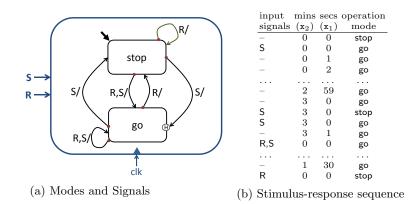

Consider a StopWatch that constantly displays timing information in minutes and seconds. This StopWatch has two operation modes (stop and go), two input signals (S and R) and a global clock that ticks every second. In the go mode the StopWatch counts time in minutes and seconds from the ticks of the clock while in the initial stop mode the timing information is kept unchanged. Initially, minutes and seconds counters are reset to 0. Signal S switches the StopWatch from one mode of operation to the other. When the StopWatch enters or re-enters the go mode, the time counting resumes on the next tick forwards from the current values of the counters. The input signal R forces counting re-initialisation to 0. If R is present alone (without S) then the StopWatch gets into the stop mode. Otherwise, when R and S are present simultaneously, the StopWatch enters immediately the go mode as Fig. 2a suggests. As a concrete example Fig. 2b presents a possible response sequence of the SR StopWatch where rows correspond to time slices of a clock ticking every second.

Fig. 2. SR StopWatch

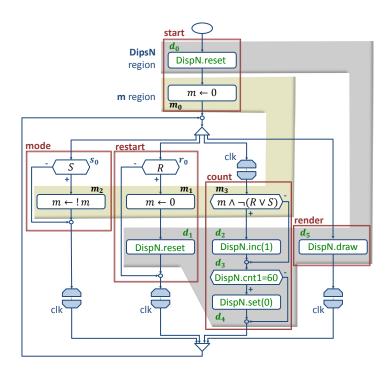

The SR StopWatch implementation of Fig. 3 is supported by the following clock–synchronised shared objects, *i.e.*, structures encapsulating data and methods that can be accessed by various concurrent threads:

Fig. 3. SR StopWatch implementation

- m acts as a variable that stores the actual operation mode. Its internal state is determined by a *bit* where *bit* = 0 indicates the **stop** mode and *bit* = 1 is for the go mode. Object m has a read method to access its current state. Besides m can be initialised *explicitly* with method init(v) where  $v \in \{0, 1\}$ and the state of m can be toggled with method update. For brevity, in Fig. 3, we write m instead of m.read == 1,  $m \leftarrow v$  in place of m.init(v) and  $m \leftarrow !m$ for m.update.

- R and S which operate as pure input signals like in SP have an internal *status* that can be *present* or *absent*. All signals are *implicitly* initialised to the default *absent* status at the beginning of each instant, that is every time the clock ticks. Method emit sets the signal status to present and method test returns true or false depending on whether the signal status is present or not. For the signals in Fig. 3, we write R or S instead of R.test or S.test,

respectively. Note that the expression  $m \land \neg(R \lor S)$  in node  $m_3$  is a shorthand for the conditional: m.read == 1 and not (R.test or S.test).

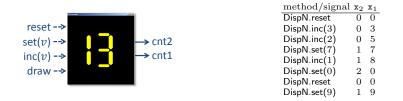

- Clock-synchronised object DispN is used to keep and display timing information. It maintains to integers  $\mathbf{x}_1$  and  $\mathbf{x}_2$  in its internal state. The values of  $\mathbf{x}_1$  and  $\mathbf{x}_2$  can be read through the methods cnt1 and cnt2, respectively. It is also possible to render both numbers in a display by calling the draw method or re-initialise both to 0 by calling the reset method. In addition, method set(v) assigns the value v to  $\mathbf{x}_1$  and, at the same time, adds 1 to the current value of  $\mathbf{x}_2$ . The idea is that  $\mathbf{x}_2$  counts the number of times that set has occurred since the last reset. On the other hand, method inc(v) increases the value of  $\mathbf{x}_1$  by v but otherwise leaves  $\mathbf{x}_2$  unaltered. As an illustration Fig. 3.1 shows an interaction sequence with object DispN.

Fig. 4. Clock-synchronised object DispN

The SR StopWatch implementation begins with a single sequential thread labelled start in Fig. 3 which explicitly initialises objects DispN and m, *i.e.*, the internal *bit* of m and the two variables  $x_1$  and  $x_2$  of DispN are set to 0. Then, the computation forks in the following four concurrent threads:

- mode: If signal S is detected to be present in node  $s_0$ , this thread changes the operation mode (go, stop) by toggling the internal *bit* of object m in node  $m_2$ . Note that the nodes labelled clk indicate the control points where the threads synchronise with the global clock tick.

- restart: In this thread, DispN and m are re-initialised in nodes  $m_1$  and  $d_1$ , respectively, every time signal R is present.

- **count**: This thread carries on the timing calculation by first considering the increment in seconds and then, sequentially after but in the same instant, adjust the number of minutes if required. Specifically, at every clock tick,  $\mathsf{DispN.inc}(1)$  in node  $d_2$  increases by 1 the number of seconds (stored in  $x_1$ ) but just as long as the actual mode is go and signals S and R are both absent as it is verified in node  $m_3$ . Otherwise, when S or R are present, we know that either the computation has just been stopped or it has just been restarted in the present instant. The former means that  $x_1$  cannot be modified since

time is frozen. The later implies that the increment of  $\mathbf{x}_1$  must only occur after exactly one second has elapsed, that is at the next instant. This also explains why **count** is placed after the initial tick (*i.e.*, after a clk node), namely counting only starts when the first second has elapsed. Then, every 60 seconds, as DispN.cnt1 = 60 checks, the execution of DispN.set(0) resets  $\mathbf{x}_1$  (seconds) to 0 and increases  $\mathbf{x}_2$  (minutes) by 1 as required.

render: This thread thread invokes method draw of DispN so that the current counting information is displayed at each tick.

The SR StopWatch codification in the DCoL language is presented in Fig. 5.

```

module StopWatch

Signal R,S

SC m

Display DispN

DispN.reset ;

m.init(0);

rec loop.

-mode -

s = S.test;

if s then m.update else skip ;

pause

- restart -

r = \mathsf{R}.\mathsf{test};

if r then m.init(0) ; DispN.reset else skip ;

pause

Ш

- count -

pause ;

m = m.read;

s = S.test;

r = \mathsf{R}.\mathsf{test};

if m == 1 and not(s \text{ or } r) then DispN.inc(1) else skip ;

c_1 = \text{DispN.cnt1};

if c_1 == 60 then DispN.set(0) else skip

Ш

- render -

Dispn.draw ;

pause ;

loop

```

Fig. 5. The SR StopWatch in DCoL syntax

As with any concurrent system, problems arise when statements accessing the same shared object interfere with each other causing nondeterminacy, metastability, data races, *etc.* This is so even when the method calls are considered to be atomic and the system is globally synchronous. Clearly, synchrony (tick alignment) can help in some cases, *e.g.*, in Fig. 3 any conflict between nodes  $d_4$  and  $d_5$  disappears in the first instant because  $d_4$  cannot be executed then. Other times, complementary conditionals eliminate any problem by making accesses mutually exclusive, *e.g.*, nodes  $d_1$  and  $d_2$  of Fig. 3 are guarded respectively by the presence and absence of signal R. There are also situations in which methods are *confluent* (also called *independent*) meaning that they can be executed in any order from any memory state without affecting the final object state, *e.g.*, nodes  $d_3$  and  $d_5$  in Fig. 3 are confluent (commute) since both read but do not modify the internal state of DispN. Observe that the confluence of  $d_3$  and  $d_5$  is a property of DispN.

A more general form of *natural* confluence occurs in methods of different objects (acting on disjoint parts of the shared state) that do not communicate, *e.g.*, methods in nodes  $m_2$  and  $d_1$  of the StopWatch which exclusively interact with objects m and DispN respectively are confluent in this general sense. In Fig. 3, accesses to objects m and DispN appear in their corresponding region. The idea is that methods belonging to different regions are all confluent. For clarity, the S region, *i.e.*,  $\{s_0, m_3\}$ , and the R region, *i.e.*,  $\{r_0, m_3\}$ , are not depicted in the figure. On the other hand, strict sequential composition, meaning no reorders due to optimisations or otherwise, makes also conflicts disappear *e.g.*, the execution of nodes  $d_2$  and  $d_3$  is conflict free if statements are always executed sequentially in the order they are listed in the code.

Despite all these positive situations, there are still object accesses in the program which lead to nondeterministic behaviours, *e.g.*, execution of  $m_1$  followed by  $m_2$  results in the **go** mode but the execution of  $m_2$  and then  $m_1$  gives the **stop** mode. Consequently computations need to be organised in a more systematic way in order to ensure *determinate* program responses. This report deals with this problem. We frame execution orderings of concurrent synchronous computations by means of a *precedence relation*. In principle, this relation indicates which method (if any) could be executed now and which one can be scheduled next. The two extreme cases of this precedence relation are: (i) a static, linear and total order of statements and (ii) a complete scheduling freedom. In the former case, the determinacy problem gets solved by the programmer in a manner that is essentially equivalent to codifying a purely sequential program. The latter reduces to an empty precedence relation so determinacy can only be preserved if all concurrent accesses to share objects are confluent to each other.

In the general scheme proposed in this work, each individual object is equipped with its own *policy*. The intention of these local policies is to expose internal object confluences. Intuitively, a policy is a locking mechanism to organise concurrent accesses to the object methods in such a way that the determinacy of the object reaction is preserved.

#### **3.2** Lift Controller – Extended Example

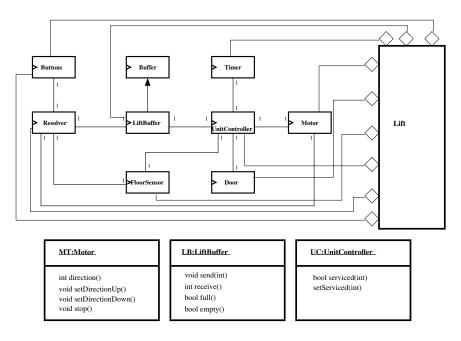

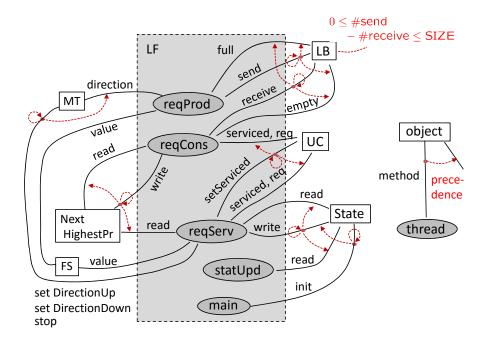

Fig. 6. Class diagram of a lift controller. The triangles in the classes signify that these are clocked synchronous. Lift is the top-level aggregation of its components. For three shared objects MT::Motor, LB::LiftBuffer and UC::UnitController methods are shown.

Our second extended example motivating the use of clock-synchronised objects subjected to synchronisation policies is a lift controller adapted from [52]. A class diagram is presented in Fig. 6. The main object is the Lift which is *active*, as it implements the overall multi-threaded control logic, in the sense of [13]. Threads in the Lift operate on various *passive* objects in the sense of [13], which may be language-, library- or user-defined. We describe the active control implemented by Lift through its main thread and four concurrent tasks, a request producer reqProd, a request consumer reqCons, a request server reqServ and a status update thread statUpd. These threads and their interaction through shared objects are seen in Fig. 7. The threads are pictured as ellipses and objects. Objects accessed only by a single thread are omitted from Fig. 7.

The Active Main Object. We present below on pages 15–17 a sketch of the lift controller example using  $C^{++}$  style syntax with DCoL extensions to enable concurrent interactions between clock synchronised shared objects. The while

loops  $while(c.m()){P}$  are an abbreviation for

and the  $switch(C)\{...\}$  branching is representable by nested conditionals in the obvious way.

Line 1 includes a header file that supports input/output. Lines 2-7 define some constants. We abstractly define the Lift class, which has a single entry point in the main() method (lines 14–82). At the start of this method, the interface objects are defined (lines 14–17), shared variables are declared (lines 18–21), and the object instances are created (lines 22–28). These objects are analogous to passive objects and concurrency is elicited by explicitly forking Esterel-style threads using the  $\parallel$  construct. The DCoL program is contained in lines 30–82, consisting essentially of an infinite loop in which the four threads reqProd, reqCons, reqServ and statUpd are running side-by-side.

```

1 #include<iostream.h>

2 #define N 1000

3 #define IDLE 0

4 #define UP 1

5 #define DOWN 2

6 #define DOOROPEN 3

7 #define TIMEOUTVAL 15

8 public class Lift{

// This is an aggregation of the objects in Figure 1

9

// Details omitted due to space constraints

10

11 }

12 // The main entry point of the OO program

13 int main(){

14 // Interface

input BB: Buttons;

15

input FS: int=0; // FloorSensor

16

output StoppedAtFloor: int=0;

17

18 // Variables

int Direction=0, CurrentFloor=0, HighestPriority=0,

19

NextHighestPriority=0;

int State=IDLE;

20

BitVector PendingReq = new BitVector(); // library object

^{21}

22 // Object instances

Resolver RR = new Resolver();

23

LiftBuffer LB = new LiftBuffer();

^{24}

UnitController UC = new UnitController();

25

Timer TT = new Timer(TIMEOUTVAL);

26

Motor MT = new Motor();

27

Door DR = new Door();

28

^{29}

while(1){

30

// Request producer thread (reqProd)

31

while(!LB.full()){

32

if(BB.present()){

33

```

| 34 | <pre>int Direction = MT.direction(); //UP=1,DOWN=-1,STOP=0</pre>                                   |  |  |

|----|----------------------------------------------------------------------------------------------------|--|--|

| 35 | <pre>int CurrentFloor = FS.value();</pre>                                                          |  |  |

| 36 | <pre>PendingRequest.update(BB.value());</pre>                                                      |  |  |

| 37 | <pre>int HighestPriority = RR.resolve(PendingRequest.value     (), Direction, CurrentFloor);</pre> |  |  |

| 38 | PendingRequest.remove(HighestPriority);                                                            |  |  |

| 39 | LB.send(HighestPriority);                                                                          |  |  |

| 40 | }                                                                                                  |  |  |

| 41 | pause;                                                                                             |  |  |

| 42 | }                                                                                                  |  |  |

| 43 | pause;                                                                                             |  |  |

| 44 |                                                                                                    |  |  |

| 45 | // Request consumer thread (reqCons)                                                               |  |  |

| 46 | while(!LB.empty()){                                                                                |  |  |

| 47 | <pre>NextHighestPriority = LB.receive();</pre>                                                     |  |  |

| 48 | while(!UC.serviced(NextHighestPriority)){                                                          |  |  |

| 49 | pause;                                                                                             |  |  |

| 50 | }                                                                                                  |  |  |

| 51 | }                                                                                                  |  |  |

| 52 | pause;                                                                                             |  |  |

| 53 |                                                                                                    |  |  |

| 54 | // Request servicing thread (reqServ)                                                              |  |  |

| 55 | while(!UC.serviced(NextHighestPriority)){                                                          |  |  |

| 56 | pause;                                                                                             |  |  |

| 57 | <pre>switch(State){</pre>                                                                          |  |  |

| 58 | <pre>IDLE: MT.stop(); DR.close();</pre>                                                            |  |  |

| 59 | if(NextHighestPriority == FS.value()) State=IDLE;                                                  |  |  |

| 60 | if(NextHighestPriority > FS.value()) State=UP;                                                     |  |  |

| 61 | if(NextHighestPriority < FS.value()) State=DOWN;                                                   |  |  |

| 62 | break;                                                                                             |  |  |

| 63 | <pre>UP: MT.setDirectionUp(); DR.close();</pre>                                                    |  |  |

| 64 | <pre>if(NextHighestPriority &gt; FS.value()) State=UP;</pre>                                       |  |  |

| 65 | if(NextHighestPriority == FS.value()) State=DOOROPEN;                                              |  |  |

| 66 | break;                                                                                             |  |  |

| 67 | <pre>DOWN: MT.setDirectionDown(); DR.close();</pre>                                                |  |  |

| 68 | <pre>if(NextHighestPriority &lt; FS.value()) State=DOWN;</pre>                                     |  |  |

| 69 | if(NextHighestPriority == FS.value())                                                              |  |  |

| 70 | break;                                                                                             |  |  |

| 71 | <pre>DOOROPEN: MT.stop(); DR.open(); TT.start();</pre>                                             |  |  |

|    | <pre>StoppedAtFloor.emit(NextHighestPriority);</pre>                                               |  |  |

| 72 | <pre>while(!TT.timeout()) pause;</pre>                                                             |  |  |

| 73 | <pre>DR.close(); State=IDLE;</pre>                                                                 |  |  |

| 74 | <pre>UC.setServiced(NextHighestPriority); break;</pre>                                             |  |  |

| 75 | }                                                                                                  |  |  |

| 76 | }                                                                                                  |  |  |

| 77 | pause;                                                                                             |  |  |

| 78 |                                                                                                    |  |  |

| 79 | // Status updating thread (statUpd)                                                                |  |  |

| 80 | <pre>cout&lt;&lt;"The current status of the lift"&lt;<state<<"\n";< pre=""></state<<"\n";<></pre>  |  |  |

| 81 | pause;                                                                                             |  |  |

82 } // end of while(1)

83 } // end of main

Request Producer (reqProd). Requests from the users are entered through a BB::Buttons object. BB has a boolean status of *present* or *absent*. A button press event sets the status to present. The status can be obtained with the BB.present method, returning true if the signal is present and returns false otherwise. BB also carries a value coding the button that is pressed which can be read using the BB.value method. Each time BB is pressed, the RR.resolve method of a request resolver object RR is called to return the next highest priority request to be serviced. This is based on position information extracted from a signal FS::FloorSensor by calling FS.value, and direction information from the motor component MT::Motor via MT.direction. The highest priority requested floor is stored via LB.send in a bounded capacity priority queue LB::LiftBuffer, which is implemented by extending a generic Buffer. The LB stores the pending requests to be serviced in a priority order. A method LB.full tests for available space in the buffer.

To prevent loosing requests, reqProd preserves the incoming requests in a bit vector called PendReq which abstracts a special memory with methods PendReq.update, PendReq.value and PendReq.remove

Request Consumer. The reqCons thread picks up the requests from LB one after the other using LB.empty and LB.receive and places them into a variable NextHighestPr until they are serviced. The service status of the active request is communicated through an object UC::UnitController which acts like a valued signal with a boolean status of *present* or *absent*. A UC.SetServiced event from the servicing thread reqServ sets the status to present. The status can be polled with the UC.serviced method, returning true if a request has been serviced and false otherwise. UC also communicates the last serviced request which can be read using the UC.req method.

*Request Server.* The actual servicing of an active request is modelled as a state machine which is implemented by a request server thread, called reqServ. Depending on a state variable State with values IDLE, UP, DOWN and DOOROPEN it moves the lift to the appropriate floor. This is done by controlling the direction of MT::Motor with methods MT.setDirectionUp, MT.setDirectionDown and MT.stop. When the lift arrives at the requested floor, observable from FS.value, then reqServ opens and closes the door DR::Door for which it accesses methods DR.close and DR.open. The opening time is determined by a timer TT::Timer which can be started with TT.start and polled via TT.timeout. The current service status of NextHighestPr is communicated back to the reqCons thread via UC.setServiced.

*Status Update.* Finally, the sole purpose of the fourth thread in Lift, called statUpd is to read the current State and output it to some environment display.

In [13] the authors introduce a classification of how concurrency is managed in OO programs. This classification contrasts *passive objects* from *active objects*. The passive approach considers threads and objects to be distinct. The task of safe threading is delegated to the programmer (i.e. the *synchronize* keyword in Java). Active objects, on the other hand, intertwine the concept of threading with objects. Here an object is allowed to invoke methods concurrently. The focus of the current article is on the safe threading using passive objects. In particular, we investigate the problem of *determinacy* of passive objects that encapsulate *reactive computation*.

Fig. 7. Threads and Shared Objects in the Lift Controller.

**Potential Data Races due to Shared Objects.** Fig. 7 illustrates how the OO specification of a simple reactive program may generate concurrent threads tangled up via shared objects. Even if we assume that there are no hidden couplings between objects and all method calls are executed atomically ("Java synchronised"), a free unmarshalled execution falls prone to data races. Since a method call is both a read and a destructive update, the result of every method call in general depends on the order in which it is executed in relation to other calls on the same object. Where this order is not fixed, because of concurrency, non-determinacy may result.

Suppose x = FS.value is the reading from reqProd and y = FS.value that of reqServ. While the lift moves up between floor 2 and floor 3 the concurrent reads x = FS.value  $\parallel y = FS$ .value may either return values x = 2 and y = 3

or x = 3 and y = 2, depending on the scheduling order. Both threads now have different views of which floor they are at. The brute force fix is to prohibit the concurrent reading of FS which breaks the modular structure of our design. A better solution is to synchronise FS with both threads reqProd and reqServ. Using the SP approach we break up the interactions into reaction macro steps (synchronous instant) using a clock and make sure that FS.value is constant during each reaction step. Such FS we call coherent for its interface because it maintains determinate behaviour for concurrent method calls during each macro step. Its value of FS.value can only change with the clock tick and distinct concurrent readings cannot be confused as they belong to different steps. Concretely, if pause denotes the clock synchronisation operation, then the reading x = 2 and y = 3 can only occur for (x = FS.value; pause)  $\parallel$  (pause; y = FS.value). This is perfectly ok, because now both threads can disambiguate the readings x = 2and y = 3 as belonging to different steps. Note that it does not matter whether pause is linked with any physical clock or not.

Factorising coherence through a clock can be applied to concurrent method calls on the other shared objects, too. For instance, consider the competition between regProd and regServ in the access of the motor MT. Suppose the lift is moving down and regServ controls the motor to stop and then move up. MT.stop; MT.setDirectionUp while reqProd is reading the direction with x =MT.direction. Then, depending on the interleaving of the concurrent composition  $(MT.stop; MT.setDirectionUp) \parallel x = MT.direction the thread reqServ may see any$ of x = DOWN, x = STOP or x = UP. This may have the effect that the servicing of a user request depends on the internal timing of the thread scheduling. This is not perhaps an issue for the user of the lift but a nightmare for program debugging. Again a clock can help to prevent reqProd from reading the motor direction at the "wrong" moments. There are many OO ways to do this. Yet, to be sure that this is schedule-independent and does not introduce deadlocks, the most reliable approach is again to factorise the problem through synchronous steps. To resolve the conflict between reading and update, we require that the updates {MT.setDirectionUp, MT.setDirectionDown, MT.stop} take *precedence* over any concurrent read MT.direction, within each step. This scheduling constraint is indicated by the dashed arrows in Fig. 7. We call these the *policy* imposed by the object MT which guarantees coherence in the sense that all concurrent calls not related by a precedence constraint are free and always return determinate results.

Where a precedence exists, the *policy-conformant* scheduler must follow the specified ordering. If there is a policy-conformant schedule we call the program *policy-constructive*. For instance, MT.setDirectionUp  $\parallel x = MT.direction$  is policy-constructive and deterministically scheduled as MT.setDirectionUp; x = MT.direction because of the precedence. If the program prescribes a sequential ordering already, as in x = MT.direction; MT.setDirectionUp, it is policy-conformant to execute exactly as stated, irrespective of the precedence. The same applies to the "self-precedences" indicated as an arrow in Fig. 7 around the update methods of MT. These precedences say that it is not permitted to call two updates

from *concurrent* threads. For instance, MT.stop || MT.setDirectionUp cannot be scheduled in a policy-conformant way: No matter the ordering, we are violating a precedence. Of course, this makes sense because *concurrent* updates introduce non-determinacy. If both calls are separated by a clock barrier, however,  $x = MT.stop \parallel$  (pause; MT.setDirectionUp) the program is policy-constructive again. Since the precedences only affect *concurrent* calls, if two updates are called *sequentially* from the *same* thread, we have nothing to worry. The program  $x = MT.direction \parallel$  (MT.stop; MT.setDirectionUp) is policy-constructive and scheduled MT.stop; MT.setDirectionUp; x = MT.direction.

The remaining shared objects in our Lift example are LB, UC and State. Policies for UC and State follow the same principle: Any two method calls that cannot be called *concurrently* with determinate result, must have a precedence fixed between them. If not, the object must ensure coherence. Here, we motivate two further aspects, viz. admissibility and the fact that policies can depend on the call history. Consider the data races occurring for the shared buffer LB. In general, the LB.full and LB.empty checks are each conflicting with value retrieval LB.receive and value addition LB.send since the latter can change the result of the former. It is natural to decree that sending and receiving always take precedence over any testing of the filling state. Also, any two LB.send and any two LB.receive must be sequentialised. These precedence relations are seen in Fig. 7. If these precedences are observed (within each macro step) then LB.send and LB.receive are independent and can occur in any order and number, provided the capacity limits are observed. To this end, the policy of LB must expose an *admissibility* constraint that at any moment the difference in the accumulated number of sends and receives (#LB.send - #LB.receive) is greater than 0 and smaller than the buffer capacity SIZE. In this way, the policy blocks any LB.send on a full and LB.receive on an empty buffer. Blocking is avoided in the program by reqProd checking LB.full and regServ checking LB.empty.

As far as we are aware, there is currently no programming language, neither OO nor SP, that would permit programming the lift controller directly in this fashion. In SP, which is our target here, the programmer must recode the object structure using standard modules and signals as the only on-board mechanisms for thread communication. E.g., BB and FS could be directly coded as Esterel-style valued signals. The state variable State however is not an Esterel signal of any kind [51] because it is shared *and* destructively updated during a tick. Instead, we could use the more liberal sequentially constructive variables of SC-CEst [46]. However, for complex objects such as the motor MT or the buffer LB neither Esterel signals or SCEst variables are sufficient. Both are ADTs encapsulating a complex behaviour, which may even wrap external program code. In the following we introduce a semantical setting to reconstruct and extend SP languages via the policy mechanism.

#### 4 Synchronous Object Policies

In this section we introduce the notion of object policies as the core synchronisation mechanism for our DCoL language. In particular, we demonstrate that the generic policy model can be instantiated to integrate several forms of constructiveness developed in the literature for synchronous languages such as Berry constructiveness of Esterel [9,43] or sequential constructiveness as introduced in the SCCharts/SCL language [56].

#### 4.1 Policies and Policy-conformant Scheduling

As a shared object c is accessed by method calls during an instant, it changes its *status* in a *policy domain*  $\mathbb{PC}_{c}$ . The status contains constructive information necessary to synchronise the method calls under an object-specific synchronisation policy. The policy expresses a constraint on the object statuses admissible in the life cycle of the object during an instant. It acts as a contract between the object and its environment. Under the assumption that the environment accesses the object only in a policy-conformant way, the object guarantees internal coherence which implies determinacy of its reaction.

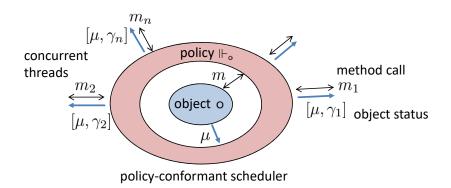

Fig. 8. Policy-conformant scheduler  $\Vdash_c$  as a wrapper shield to control accesses to object c from concurrent threads.

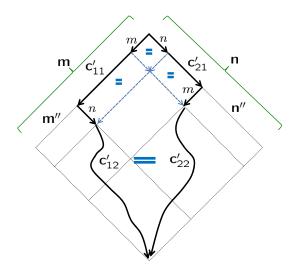

The elements of the policy domain  $\mathbb{PC}_{c}$  contain constructive information about the history and predicted future of method calls on c. The history is determined by the sequence of accesses already performed on the object. The future refers to the method calls which can still potentially be executed on cby the concurrent environment. We structure object statuses  $\varphi \in \mathbb{PC}_{c}$  as formal intervals  $\varphi = [\mu, \gamma] \in \mathbb{PC}_{c} = \mathbb{P}_{c} \times \mathbb{C}_{c}$ . The "lower bound"  $\mu \in \mathbb{P}_{c}$  is the history part containing *must* information. It expresses what accesses the object has seen already. The "upper bound"  $\gamma \in \mathbb{C}_{c}$  is the *can* information which predicts the possible future status of the object due to method calls that are still outstanding in the concurrent environment. An interval  $\varphi$  codifies an "envelope of control" for determinate and policy-conformant run-time scheduling. Suppose, at some moment in the scheduling, the currently active threads try to execute method calls  $m_i$  on object c. Each thread sees the same must status  $\mu$  but different can information  $\gamma_i$ , since these record the potential future activities of all other threads. Hence, an interval  $[\mu, \gamma]$  should be thought of a thread-local interface to the object. This is illustrated in Fig. 8.

This two-sided interval structure of object statuses generalises Berry's constructive must-can semantics for Esterel [9]. Technically, we assume update operations  $\mu \odot m$  and  $m \odot \gamma$  where  $m \in M_c$  is a method name on c, ignoring any parameter passed with the call and also any value returned by the object. Then, the execution of a method call m(v) in the concurrent environment would change the observable status of c from  $[\mu, m \odot \gamma]$ , where m lies in the future, to the status  $[\mu \odot m, \gamma]$  where m is added to the history. This amounts to a monotonic increase  $[\mu, m \odot \gamma] \sqsubseteq_c [\mu \odot m, \gamma]$  in the information ordering  $\sqsubseteq_c$  associated with  $\mathbb{PC}_c$  (defined below in Sec. 4.5). Further operations on the prediction  $\mathbb{C}_c$ that we will need are choice  $\gamma_1 \oplus \gamma_2$  for non-deterministic over-approximation of program branching, concatenation  $\gamma_1 \cdot \gamma_2$  for sequential composition and the interleaving product  $\gamma_1 \otimes \gamma_2$  for parallel composition of program context.

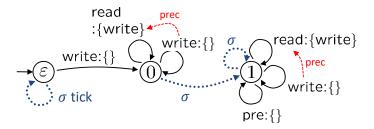

Here we study domains  $\mathbb{PC}_{c}$  generated from the class of *policies* defined below in Def. 1. Let M<sub>c</sub> be the methods of object c. A policy for c is a safety and liveness property modelled using a deterministic state machine  $\Vdash_{c}$  with a set of control states  $\mathbb{P}_{c}$  and distinguished start state  $\varepsilon \in \mathbb{P}_{c}$ . The call of a method leads to a change of the control state. From a control state only a set of methods are admissible. We write  $\mu \Vdash_{c} \downarrow m$  to express that  $m \in M_{c}$  is admissible in state  $\mu \in \mathbb{P}_{c}$ . An admissible *m* can be executed if there is no other admissible method in the concurrent environment that has a higher precedence from the current state. We write  $\mu \Vdash_{c} m' \to m$  to express that m' has precedence over m in state  $\mu$ . When such m' is concurrently executable, m has to be delayed. Otherwise, m can be executed whereupon the policy takes a transition to a new control state  $\mu \odot m \in \mathbb{P}_{c}$ . Note that  $\mu \Vdash_{c} m' \to m$  implies  $\mu \Vdash_{c} \downarrow m$  and  $\mu \Vdash_{c} \downarrow m'$ . If two methods m and m' are admissible and none takes priority over the other, then both can be executed in any order with the same resulting state  $\mu \odot m \odot m' = \mu \odot m' \odot m$ . In addition to transitions enabled by methods, every policy machine has a special *tick* transition  $\sigma \in \mathbb{P}_{c} \to \mathbb{P}_{c}$  to mark the completion of the current synchronous instant. The presence of a  $\sigma$ -transition indicates that the instant can be paused in this state. The formal definition of precedence policies is given in the following Def. 1.

**Definition 1.** A policy for object c with method names  $M_c$  is a state machine  $\Vdash_c = (\mathbb{P}_c, \varepsilon, \to)$  consisting of a set of control states  $\mathbb{P}_c$ , an initial state  $\varepsilon \in \mathbb{P}_c$ and a labelled transition relation  $\to \subseteq \mathbb{P}_c \times L_c \times \mathbb{P}_c$  with action labels  $L_c = (M_c \cup \{\sigma\}) \times 2^{M_c}$ . Instead of  $(\mu_1, (a, L), \mu_2) \in \to$  we write  $\mu_1 - a: L \to \mu_2$ . We then say action a is admissible in state  $\mu_1$  and it is blocked by all  $m \in L$ . When the blocking set L is irrelevant we drop it and write  $\mu_1 - a \rightarrow \mu_2$ . A policy must always satisfy the Determinacy, Confluence and Maximal Progress conditions:

- Determinacy: If  $\mu$  -a: $L_1 \rightarrow \mu_1$  and  $\mu$  -a: $L_2 \rightarrow \mu_2$  then  $L_1 = L_2$  and  $\mu_1 = \mu_2$ .

- Confluence: If  $\mu a_1: L_1 \rightarrow \mu_1$  and  $\mu a_2: L_2 \rightarrow \mu_2$  are method calls which do not block each other, i.e.,  $a_2 \in M_c \setminus L_1$  and  $a_1 \in M_c \setminus L_2$ , then for some  $\mu'$  both  $\mu_1 - a_2 \rightarrow \mu'$  and  $\mu_2 - a_1 \rightarrow \mu'$ .

- Maximal Progress: If  $\mu a \rightarrow \mu_1$  and  $\mu \sigma: L \rightarrow \mu_2$ , then  $a \in L \cup \{\sigma\}$ .  $\Box$

Notation. We exploit the determinacy for actions  $a \in \mathsf{M}_{\mathsf{c}} \cup \{\sigma\}$  and write  $\mu \odot a$  for the unique  $\mu'$  such that  $\mu - a \rightarrow \mu'$ , if it exists. It is convenient to identify a method sequence  $\mathbf{m} \in \mathsf{M}^*_{\mathsf{c}}$  with the policy state  $\varepsilon \odot \mathbf{m} \in \mathbb{P}_{\mathsf{c}}$  that is reached by executing  $\mathbf{m}$  in the policy automaton. Transition function  $\odot$  is extended to sequences  $\mu \odot \mathbf{m}$  by induction, i.e.,  $\mu \odot \varepsilon = \mu$  and  $\mu \odot (m \mathbf{m}) = (\mu \odot m) \odot \mathbf{m}$ .

We write  $\mu \Vdash_{c} \downarrow m$  to state that m is admissible in state  $\mu$ , i.e.,  $\mu - m \to \mu'$  for some  $\mu' \in \mathbb{P}_{c}$ . Further,  $\mu \Vdash_{c} m_{1} \to m_{2}$  expresses that in state  $\mu$  an admissible method  $m_{1}$  has precedence over another  $m_{2}$ , i.e.,  $\mu \Vdash_{c} \downarrow m_{1}, \mu - m_{2}:L_{2} \to \mu'$ and  $m_{1} \in L_{2}$ . Further, we let  $\mu \Vdash_{c} m_{1} \diamond m_{2}$  stand for  $\mu \Vdash_{c} \downarrow m_{1}, \mu \Vdash_{c} \downarrow m_{2}$ and both  $\mu \nvDash_{c} m_{1} \to m_{2}$  and  $\mu \nvDash_{c} m_{2} \to m_{1}$ . We say that  $m_{1}$  and  $m_{2}$  are *concurrently enabled* in state  $\mu$ . In this notation, the confluence property says that if  $\mu \Vdash_{c} m_{1} \diamond m_{2}$  then  $\mu \odot m_{1} \Vdash_{c} \downarrow m_{2}, \mu \odot m_{2} \Vdash_{c} \downarrow m_{1}$  and  $\mu \odot m_{1} \odot m_{2} =$  $\mu \odot m_{2} \odot m_{1}$ . Finally, we write  $\mu \Vdash_{c} \downarrow m$  if m is executable from state  $\mu$ , i.e.,  $m = \varepsilon$  or  $m = m m', \mu \Vdash_{c} \downarrow m$  and  $\mu \odot m \Vdash_{c} \downarrow m'$ . If  $\mu \Vdash_{c} \downarrow m$  we also denote the final state as  $\mu \odot m$  and say that method sequence m is *admissible* and state  $\mu \odot m$  is *reachable*.

Note that a state with  $\mu \not\Vdash_{c} \downarrow m$  for all  $m \in M_{c}$  is a *policy error* state since it has no outgoing transitions. In this case  $\mu \Vdash_{c} \downarrow m$  iff  $m = \varepsilon$ . Like in safety automata, once an accepted sequence of actions m is an error, all its extensions m m, for any  $m \in M_{c}$ , are rejected, too.

The policy as a contract between the object and the scheduler indicates to the scheduler if and when methods can be called concurrently without jeopardising determinacy of the object's reaction. Specifically, if  $\mu \Vdash_{c} m \diamond n$ , then the object guarantees that the order in which methods m and n are executed is immaterial. This is reflected in the fact that the resulting policy states  $\mu \odot m \odot n$  and  $\mu \odot n \odot m$  are identical.

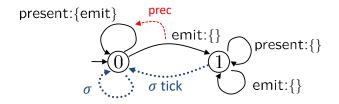

**Example 1.** The policy automaton for Esterel's pure signals is given in Fig. 9. Esterel valued signals are discussed below in Sec. 5. A pure signal **s** can assume one of two control states, *absent* (0) or *present* (1), i.e.,  $\mathbb{P}_{s} = \{0, 1\}$ . The methods of **s** are  $M_{s} = \{\text{present}, \text{emit}\}$ . A signal becomes present upon execution of the emit method and if no emit is executed the signal is absent by default. Hence the start state of the signal policy is  $\varepsilon = 0$ . There is no method to "unemit" (unlike with SCEst [46]), instead, each signal status reset to 0 with the clock

Fig. 9. Esterel Pure Signal Policy.

tick, i.e.,  $\sigma(\mu) = 0$ . A thread can read the status with the present method. Methods are always admissible,  $\mu \Vdash_{s} \downarrow m$  for all  $\mu \in \mathbb{P}_{s}$  and  $m \in M_{s}$ , but are subjected to a stateful precedence. A presence test on a signal that is not emitted yet has to wait for pending emissions to take place. This is achieved by giving emit precedence over present, i.e.,  $0 \Vdash_{s} \text{emit} \rightarrow \text{present}$ . As a result, emit and present are not confluent in state 0, i.e.,  $0 \nvDash_{s} \text{emit} \diamond$  present. This makes sense, because no signal is emitted yet. While in state 0, the order of method execution is crucial: If present is executed before the emit, the signal returns 0 whereas if present happens after emit we see 1. This changes after the first emit has occurred. Then the control state moves from 0 to 1 and switches off the precedence. Now both methods are confluent, i.e.,  $1 \Vdash_{s} \text{emit} \diamond$  present. Indeed, once the signal has been emitted, a present test will always see status 1, before or after any further emit. Formally, the policy automaton's transitions are  $\mu \odot \text{emit} = 1$  and  $\mu \odot \text{present} = \mu$  for all  $\mu \in \mathbb{P}_{s}$ . The control states can be identified by regular expressions,  $0 \cong \text{present}^{*}$  and  $1 \cong \text{emit} \cdot (\text{present} + \text{emit})^{*}$ .

As seen in Fig. 9, the clock tick  $\sigma$  is admissible in any state. It always takes the policy back to the start state 0. The maximal progress condition requires that the clock is blocked by all methods emanating from the same state. These precedences are implicit and omitted in Fig. 9 for simplicity. Formally, we have  $0 - \sigma: M_s \rightarrow 0$  and  $1 - \sigma: M_s \rightarrow 0$ .

**Comment on Esterel vs DCoL.** In our semantics we distinguish between sequential and concurrent object accesses. In a sequential composition P;Q everything in Q is strictly after anything in P. In a conditional<sup>11</sup> if  $s_1$ .present then P else Q all accesses in P and Q are strictly after the present test  $s_1$ .present. This is different in Esterel which does not have strict sequential ordering. As a result the two branches of a conditional can be decomposed in Esterel into a

<sup>&</sup>lt;sup>11</sup> Strictly, in our DCoL syntax we must write this as  $| \mathbf{t} v = \mathbf{s}_1$ .present in if v then P else Q because we distinguish carefully between a method call and the value v returned by it. For the present discussion this is irrelevant, however, so we do not bother.

parallel composition:

if

$$s_1$$

.present then  $P$  else  $Q$

$\cong$  if  $s_1$ .present then  $P \parallel$  if  $s_1$ .present else  $Q$  (1)

so that the program branch Q is taken to be concurrent with the present test guarding the execution of P and likewise P is considered concurrent with the presence test guarding Q. Moreover, in a single branch **if**  $s_1$ .present then P the body P is concurrent with its own guard and thus can be decomposed

if

$$s_1$$

.present then  $P$

$\cong$  if  $s_1$ .present then  $s_2$ .emit  $\parallel$  if  $s_2$ .present then  $P$ .

which makes explicit the concurrent relationship between P and the guard if  $s_1$ .present. This has the effect that if P emits  $s_1$ , then the program if  $s_1$ .present then P is rejected. In our semantics we only reject the concurrent version

$Q_1 =_{df}$  if  $s_1$ .present then  $s_2$ .emit || if  $s_2$ .present then  $s_1$ .emit

but not the direct sequential

$Q_2 =_{df}$  if s<sub>1</sub>.present then s<sub>1</sub>.emit

since in the latter the presence of  $\mathbf{s}_1$  is decided strictly before the emission is executed. The fact that  $\mathbf{s}_1$  is emitted after it has been tested to be absent is not considered a causality problem. In our setting, causality problems only exist as cyclic dependencies between *concurrent* accesses. Similarly, Esterel will reject a program  $\mathbf{s}_1$ .present; $\mathbf{s}_1$ .emit while we accept it as good, again, because the emission is happening strictly after the presence test.

Therefore, our policy in Fig 9 for Esterel signals generates a more liberal use of signals accepting more programs than Esterel, due to strict sequential ordering. In Esterel, the only sequential ordering available is through the pause construct, i.e., via the clock tick. So, when we call the policy of Fig. 9 above a policy of Esterel pure signals, then this is to be understood for the fragment of programs in which there are no sequential accesses to the same signal. An Esterel presence test presents then P can be simulated as if s.present then s'.emit  $\parallel$  if s'.present then P where s' is a fresh auxiliary signal that must not occur in P. Along the same line, an Esterel "sequential" composition P; Q can be simulated as  $P; s'.emit \parallel$  if s'.present then Q with a fresh auxiliary signal s'. This necessary recoding of Esterel is not a weakness of our language but just makes explicit the essential concurrent nature of Esterel.

We could restrict our signal policy to come somewhat closer to Esterel by making emit only admissible if there has not been a present test sequentially before. Then, a program like if  $s_1$ .present else  $s_1$ .emit or  $s_1$ .present; $s_1$ .emit would be rejected. However, it would still permit if  $s_1$ .present then  $s_1$ .emit

which Esterel would reject. Through the choice of policy we cannot and do not want to circumvent the key distinction between concurrent and sequential object accesses of DCoL.

Observe that the identification (1) is sound in Esterel only because method calls do not have any side effects. In the general setting captured by DCoL where we do not preclude side effects in method calls the equivalence (1) does not hold: two concurrent calls are not the same as one single call.

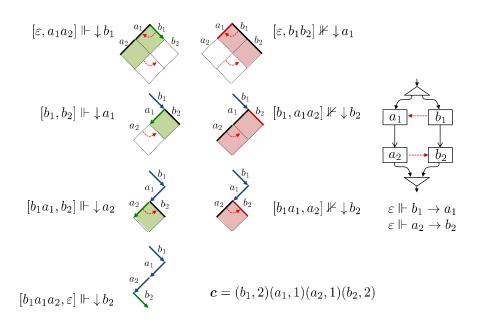

#### 4.2 Enabling

The job of the scheduler wrapper shield is to make sure that concurrent sequences of method calls are interleaved in such a way that the precedences prescribed by the object's policy are enforced. At the same time, concurrency should not be restricted unnecessarily, exploiting the available method confluences in the policy. To this end we must lift the confluence relation  $\mu \Vdash_{c} m \diamond n$  from individual methods to sequences of methods  $\mu \Vdash_{c} m \diamond n$ , executed by concurrent threads. This is done in terms of an *enabling relation*  $[\mu, m] \Vdash_{c} \downarrow n$  that explains, locally for a given thread, whether or not a sequence method calls n is confluent with a sequence of calls m to be executed in the thread's concurrent environment. This enabling relation will be an asymmetric decomposition of the confluence relation in the sense that (i) it merely implies the admissibility of  $\boldsymbol{n}$  but not of the context sequence  $\boldsymbol{m}$  and that (ii) mutual enabledness  $[\mu, \boldsymbol{m}] \Vdash_{c} \downarrow \boldsymbol{n}$  and  $[\mu, n] \Vdash_{\mathsf{c}} \downarrow m$  implies  $\mu \Vdash_{\mathsf{c}} m \diamond n$ . Our notation  $[\mu, m] \Vdash_{\mathsf{c}} \downarrow n$  for the enabling relation forms a context  $[\mu, m]$  which combines the policy state  $\mu \in \mathbb{P}_{c}$  as the history of the object (must information) and the sequence  $\mathbf{m} \in \mathsf{M}_c^*$  as a prediction of the concurrent environment (can information).

The definition of  $[\mu, \mathbf{m}] \Vdash_{c} \downarrow \mathbf{n}$  is by induction on the length on  $\mathbf{n}$ . First, consider the special case where  $\mathbf{n}$  is a single method. We have  $[\mu, \mathbf{m}] \Vdash_{c} \downarrow n$  iff method n is admissible in state  $\mu$  and cannot be blocked by precedence by any admissible execution of the environment methods  $\mathbf{m} = m_1 m_2 \ldots, m_k$ , for as long as these are not themselves blocked by n. Then, a sequence  $\mathbf{n} = n_1 n_2 \cdots n_l$  is enabled in  $[\mu, \mathbf{m}]$  if  $\mathbf{n}$  is admissibly executable from  $\mu$  and all method calls remain enabled under environment  $\mathbf{m}$ . Formally,  $[\mu, \mathbf{m}] \Vdash_{c} \downarrow \mathbf{n}$  if for all  $1 \leq j \leq l$ , we have  $[\mu \odot n_1 n_2 \ldots n_{j-1}, \mathbf{m}] \Vdash_{c} \downarrow n_j$ . Observe that  $[\mu, \varepsilon] \Vdash_{c} \downarrow \mathbf{m}$  is the same as  $\mu \Vdash_{c} \downarrow \mathbf{m}$ . Finally, two method sequences  $\mathbf{m}, \mathbf{n} \in \mathsf{M}_c^*$  are concurrently enabled in history  $\mu$ , written  $\mu \Vdash_c \mathbf{m} \diamond \mathbf{n}$ , if both  $[\mu, \mathbf{m}] \Vdash_{c} \downarrow \mathbf{n}$  and  $[\mu, \mathbf{n}] \Vdash_{c} \downarrow \mathbf{m}$ . The following definition formalises the notion of enabling in a more recursive fashion. Alternatively, the relation can be defined as the least relation closed under the rules given in Fig. 10.

**Definition 2 (Enabling).** Let *c* be an object with policy  $\Vdash_c$  on methods  $M_c$ . Further, let  $\mu \in \mathbb{P}_c$  be a policy state,  $n \in M_c$  a method and  $m, n \in M_c^*$  method sequences. Then,

1. **m** enables n in  $\mu$ , written  $[\mu, \mathbf{m}] \Vdash_c \downarrow n$ , if  $\mu \Vdash_c \downarrow n$  and either (i)  $\mathbf{m} = \varepsilon$  or (ii)  $\mathbf{m} = m \mathbf{m}'$  and if  $\mu \Vdash_c \downarrow m$  then  $\mu \nvDash_c m \to n$  and if also  $\mu \nvDash_c n \to m$ then  $[\mu \odot m, \mathbf{m}'] \Vdash_c \downarrow n$ .

- 2.  $\boldsymbol{m}$  enables  $\boldsymbol{n}$  in  $\mu$ , written  $[\mu, \boldsymbol{m}] \Vdash_{c} \downarrow \boldsymbol{n}$ , if (i)  $\boldsymbol{n} = \varepsilon$  or (ii)  $\boldsymbol{n} = n \boldsymbol{n}'$ ,  $[\mu, \boldsymbol{m}] \Vdash_{c} \downarrow n$  and  $[\mu \odot n, \boldsymbol{m}] \Vdash_{c} \downarrow \boldsymbol{n}'$ .

- 3. *m* and *n* are concurrently enabled in  $\mu$ , written  $\mu \Vdash_c m \diamond n$ , if we have both  $[\mu, m] \Vdash_c \downarrow n$  and  $[\mu, n] \Vdash_c \downarrow m$ .

$$\frac{\mu \Vdash_{c} \downarrow n}{\mu \Vdash_{c} \downarrow \varepsilon} \quad \frac{\mu \Vdash_{c} \downarrow n \quad \mu \odot n \Vdash_{c} \downarrow n}{\mu \Vdash_{c} \downarrow n n}$$

$$\frac{\mu \Vdash_{c} \downarrow n}{[\mu, \varepsilon] \Vdash_{c} \downarrow n} \quad \frac{\mu \Vdash_{c} \downarrow n \quad \mu \nvDash_{c} m \to n \quad \mu \Vdash_{c} n \to m}{[\mu, m m] \Vdash_{c} \downarrow n}$$

$$\frac{\mu \Vdash_{c} \downarrow n \quad \mu \nvDash_{c} m \to n \quad \mu \nvDash_{c} n \to m \quad [\mu \odot m, m] \Vdash_{c} \downarrow n}{[\mu, m m] \Vdash_{c} \downarrow n}$$