# Synchronized Shared Memory and Procedural Abstraction: Towards a Formal Semantics of Blech

(Version 2 - 2020/08/30)

Friedrich Gretz, Franz-Josef Grosch Bosch Corporate Research Renningen, Germany

Michael Mendler, Stephan Scheele Department of Applied Computer Sciences University of Bamberg, Germany

#### Abstract

Traditional imperative synchronous programming languages heavily rely on a strict separation between data memory and communication signals. Signals can be shared between computational units but cannot be overwritten within a synchronous reaction cycle. Memory can be destructively updated but cannot be shared between concurrent threads. This incoherence makes traditional imperative synchronous languages cumbersome for the programmer.

The recent definition of *sequentially constructive* synchronous languages offers an improvement. It removes the separation between data memory and communication signals and unifies both through the notion of *clock synchronized shared memory*. However, it still depends on global causality analyses which precludes procedural abstraction. This complicates reuse and composition of software components.

This report shows how procedural abstraction can be accommodated inside the sequentially constructive model of computation. We present the Sequentially Constructive Procedural Language (SCPL) and its semantic theory of *policy-constructive* synchronous processes. SCPL supports procedural abstractions using *policy interfaces* to ensure that procedure calls are memory safe, wait-free and their scheduling is determinate and causal. At the same time, a policy interface constrains the level of freedom for the implementation and subsequent refactoring of a procedure. As a result, policies enable separate compilation and composition of procedures.

We present our extensions abstractly as a formal semantics for SCPL and motivate it concretely in the context of the open-source, embedded, real-time language Blech.

### I. MOTIVATION & CONTRIBUTION

Production cost and energy efficiency requirements drive embedded systems towards consolidated platforms utilising multicore processing units that share common resources. Software architectures for such systems are growing in complexity and integration effort. It is imperative to maintain a deterministic and predictable interplay between software components and prevent data races or deadlocks by design, especially for safety-critical embedded systems. One

Change notes for version 2:

- fix typos, minor adjustment of method notation for consistency and to remove redundancy.

- add concept of "synchronous activity" to unify black-box semantics of methods and procedures.

- fill in some missing explanations

- extend Acknowledgements

An abridged version of this report has appeared in: Forum on Specification and Design Languages (FDL 2020), Kiel, Germany, 15-17 September 2020.

approach for synchronizing concurrent systems are classical locking mechanisms such as mutexes or spin-locks. However they are inefficient for frequent, fine-grained communication and hard to debug.

Where the focus is on control-flow, imperative synchronous programming (ISP) languages such as Esterel [1], Quartz [2], PRETC [3], ForeC [4] or Céu [5] are a good choice to develop reactive, safety-critical embedded software. Based on precise mathematical foundations, ISP utilises mechanisms such as logical clocks and clock-aligned signals for inter-module synchronization and communication. The compiler verifies determinacy by static program analysis and thus relieves the developer from the burden of manually solving synchronization problems.

However, traditional ISP languages come with rather specialised syntax and rigidly synchronized signals as the only form of decoupling, which precludes sharing of complex data structures and multiple updates within a clock cycle. While current ISP languages enable the building of complex systems through white-box [6]–[8] or grey-box [9] modules they do not properly support black-box abstraction. Notably, ".. the Esterel language has no mechanism for separate compilation or pre-compiled component libraries.." [10, p. 34]. Procedural abstractions for ISPs exist but they are not an integrated part of the source language and its well-defined semantics. The modular structures generated by compilers [11]–[13] for ISP are based on shared memory and cannot be coded in ISP itself. This makes SP programming an archane experience for main-stream programmers familiar with procedural abstractions.

Recently, the sequentially constructive model of computation, which has given rise to ISP languages such as SCCharts [8], has reconciled shared memory and signals. In [14] this approach has been extended to *policy-coherent* shared objects that can encapsulate general abstract data structures, but without considering modularisation. In this report we show that using those techniques, ISP can achieve black-box procedural abstraction on general abstract data structures. We present the core language SCPL and its structural operational semantics in a generic memory model of structured data whose coherence is protected by *policy interfaces*. An SCPL process P which is *constructive* with respect to a given interface C guarantees memory safe, deterministic and deadlock-free execution in all memory stores coherent for this interface C. Together with its interface, a pair (P, C) then constitutes a generic unit for procedural composition. A procedure can be mapped safely into another memory context C'through *interface extensions*  $f : C \subseteq C'$  that preserve policy-constructiveness. The scheduling of a procedure (P, C) in its calling context is wait-free and entirely determined by its interface  $\mathcal{C}$  and the map f. The procedure P is treated like a black-box and can be replaced by any step function functionally equivalent to (P, C). In this way, procedures operating on shared data can be assembled as first-class, black-box actions just like the reading or emission of a signal in conventional ISP. SCPL reconciles the high-level syntax of ISP with intermediate and low-level computational structures under a uniform and constructive synchronous semantics. It provides the same safety guarantees and predictability as conventional ISP but in the shared memory context familiar to main-stream programmers. It promotes synchronous programming less as a language but as a "mark-up" of conventional syntax via scheduling interfaces.

The Blech language developed at Bosch is among the first ISP languages with first-class procedures that does not depend on white-box inlining. However, there is no formal semantics for it, yet. In this report, we fill this gap. In doing so we adapt and extend the theory of [14] and provide the calculus SCPL. It can serve as an intermediate format not only for Blech but also other sequentially constructive languages, like SCCharts [8].

#### II. INTRODUCTORY EXAMPLE

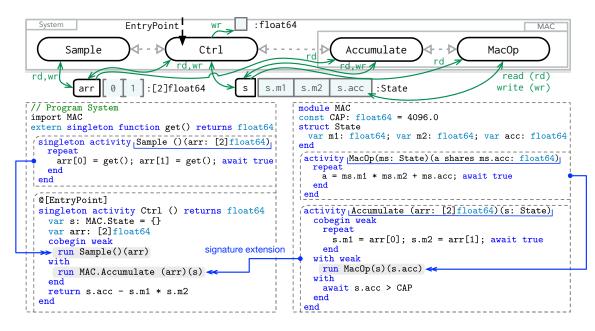

Fig. 1. Architecture and implementation of a multiply-accumulate process with procedural abstraction in pure synchronous control flow.

Let us consider a simple reactive system and its implementation in Blech to illustrate the concepts of sequentially synchronous reaction, synchronized shared memory and black-box procedural abstraction. Figure 1 depicts a reactive system in Blech syntax. System consists of two decoupled procedures (called activities in Blech) implementing a controller component Ctrl, a component Sample for external data input and imports module MAC. The latter implements a multiply-accumulate operation in software by the two decoupled procedures MacOp and Accumulate. The MAC operation in MacOp computes the product of two multipliers  $m_1$ ,  $m_2$  and adds its result to an accumulator Accumulate, i.e.,  $acc \leftarrow acc + m_1 \cdot m_2$ . Usually, MAC operations are implemented by highly-optimised circuits and are part of DSP and floating-point execution units [15], [16]

The procedures of System communicate via shared memory, passed in procedure calls by reference. Module System imports MAC and shares its data structures. Procedure Sample interacts with the external environment, providing a pair of values of type float64 fetched as inputs from the environment via external function get. Note the multiple writes to arr in one reaction. The controller Ctrl instantiates the shared data structures arr and s:Mac.State and concurrently combines calls of the activities Sample and Accumulate. Note, that Sample and Ctrl are declared as singleton, meaning that there may exist at most one instance (thread) of such a subprogram in a concurrent context. This is usually required by threads that interact directly with external or limited resources.

MAC declares the accumulator state by the structure State, i.e., by two sample values m1, m2 and the accumulator acc, typed as double precision floating-point numbers. Each procedure declares its in- and output parameters. In Blech this is expressed by two separate lists for input and output, e.g., the interface of procedure Accumulate declares arr: [2]float64 as an input that can be read and s:State as an output that can be read and written during execution. The procedure Accumulate concurrently combines the mapping of the array arr

to m1 and m2, a call of procedure MacOp(s)(s.acc) to perform the multiply-accumulate, and a third thread await s.acc > CAP to detect that acc exceeds the threshold, which triggers the forced termination of the first two threads. The preemption is indicated by indicated by the keywords weak in the cobegin parallel construct.

All activities are reaction procedures which operate in synchronous lock-step. At each tick of a global logical clock, each activity performs one iteration of its behavior until it either pauses at an await statement waiting for another cycle, or terminates by reaching the end of the activity. In the example, exactly two data samples are multiplied and accumulated into the state s during each reaction cycle, called a *macro-step*. The physical timing which relates the clock iteration and the data sampling determines how much computation can be performed during each macro-step. This needs to be calibrated by timing analysis. Assuming this is done, each reaction is considered to happen *instantaneously* in zero time (*Synchrony Hypothesis*) in the high-level semantics.

Our example implements a stream-processing function that could also be programmed in a data flow language like Lustre. Such languages can provide a higher level of abstraction when control-flow is determined by static functional relationships between signals. Yet, in many practical applications, control-flow is not static or functional and more naturally decomposed through interactions in shared memory. For instance, the Accumulate activity in Fig. 1 must terminate when the accumulated signal on s.acc surpasses a threshold value CAP. This is achieved by the watchdog thread await s.acc > CAP running in parallel with MacOp(s)(s.acc). The latter, which is labelled as a weak thread is preempted by the watchdog when the threshold condition is detected. When MAC.Accumulate terminates, then also the main activity Ctrl terminates and returns a final value. Preemption and terminating stream processes are not naturally coded in pure Lustre.

Control-flow constructs, of course, can be simulated in data flow, see e.g. SCADE [17]. Yet, this introduces the problem that efficient control-flow code exploiting shared memory and inplace destructive updates must be "rediscovered" by the compiler. Where the shared memory procedural code such as in Fig. 1 can be provided by the programmer it is often more efficient. The catch is that procedural imperative code does not give the same degree of safety guarantees that come with domain-specific languages such as Lustre, Signal or Esterel. Shared memory multi-threading introduces many tangled risks of data races and memory incoherence that seem hard to avoid. In this report we aim to show that the sequentially constructive model of synchronous computation can be applied to marshall procedural multi-threaded code in much the same way that the static analyses of domain-specific ISP languages safeguard interactions of synchronous modules.

To safegurd against memory races, Blech functions and procedures are implicitly wrapped by *policy interfaces* that specify the standard data types of their parameters, the memory access methods applied to these and their causal ordering. A policy interface acts as an assumptionguarantee contract to enable black-box abstraction and separate compilation. For instance, the declaration MacOp(ms) (a shares ms.acc) tells us that the parameter ms in the first list is read-only whereas a in the second list is potentially written. This information is used to resolve the scheduling order in Accumulate where the procedure call MacOp(s)(s.acc) is concurrent (the cobegin...with...end construct) with the watchdog testing s.acc > CAP. Assuming the data type float64 of the shared cell s.acc specifies a regular data flow variable, the policy interface of the calling site Accumulate will impose the "write-beforeread" causal order s.acc.wr ---> s.acc.rd to eliminate data races. As a consequence, the call MacOp(s)(s.acc) will be scheduled before s.acc > CAP. As scheduling precedences go, the parameter lists in Blech procedure headers are analogous to the separation between *input* and *inputoutput* signals in Esterel module interfaces. The essential difference is that Blech parameters may be destructively updated during a macro-step, which is not possible in Esterel. Because of that the MacOp interface also contains a *sharing* specification a shares ms.acc. This tells us that the procedure implements all memory accesses to a and to the substructure ms.acc of ms in a single thread. This makes it possible to alias the two parameters in the activity call MacOp(s)(s.acc) of Accumulate and perform the operation instantaneously in the same memory cell. While Esterel would detect a causal cycle, in sequentially ordered after the read s.acc.rd.

The formal mechanism to control the safe instantiation of activities is an *extension relation* on interfaces. The compiler checks that the memory mapping applied at the procedure call establishes a formal extension of the interface of the callee to that of the caller. This is indicated by the blue arrows in Fig. 1. For instance, the call MacOp(s)(s.acc) implies a mapping [s/ms, s.acc/a] of the (formal) memory paths of the callee to the (actual) paths of the caller. This aliasing is a proper extension because (i) the data types match up and (ii) the interface of the callee MacOp exports a sharing between a and ms.acc.

The use of policy interfaces for procedure instantiation and scheduling likewise applies to external procedures for which the code is not available. The external function get imported by System returns a new, different sample value each time it is called. This would induce non-determinism when called from concurrent threads. Therefore, it is flagged by the keyword singleton which is part of the policy interface of get and protects it from concurrent accesses.

Policy interfaces also actively help to resolve the scheduling order of procedure calls. For instance, in Ctrl the memory cell arr is in the output list of procedure call Sample()(arr) and at the same time in the input list of MAC.Accumulat(arr)(s). Assuming the data type arr:[2]float64 specifies a regular data flow variable, we apply the "write-before-read" causal order to eliminate data races. The "write-before-read" precedence is part of the policy interface of memory cell arr and forces Sample()(arr) to be scheduled before MAC.Accumulate(arr)(s). In a similar way, the three threads in Accumulate are scheduled with the help of policy interfaces.

#### III. THE SEQUENTIALLY CONSTRUCTIVE PROCEDURAL LANGUAGE KERNEL SCPL

The abstract syntax of SCPL is given in Fig. 2. It provides a set of core operators to represent synchronous semantics of shared memory concurrency and procedural abstractions.

A program M consists of a sequence of declarations and a pure control flow P. Declarations can be (hierarchically nested) data structures  $D_1$ , encapsulating scalar data variables and procedures  $D_2$ . All declarations are assumed to be statically resolved and thus do not nest with control flows. The grammar focuses on the pure control flow in which the sub-language of *value expressions* e is abstract, assuming side-effect free, atomic computations of (typed and possibly structured) values. Since the imperative semantics of expression evaluation can be coded in terms of regular control flow we do not need to add imperative features to the expression sub-language. Since the focus of this report is to study semantics we may

Fig. 2. Abstract syntax of SCPL main program M, declarations  $D_1$ ,  $D_2$  and control-flow statements P, where  $k \in \{0, 1, 2\}$  is a completion code, e is a pure value expression without side effects, x a value variable, o,  $o_i$  memory paths, m a method name and p a procedure name.

assume that type checking has been done and all memory structures are statically allocated and referenced via fully qualified names, which are called *memory paths*.

Control-flow is completed by the statements exit k where the completion code  $k \in \{0, 1, 2\}$  distinguishes three forms of continuation. The instance exit 0, also written nothing, instantaneously completes by *termination* and continues with any sequentially down-stream statements in the current thread. The instance exit 2, called *exit*, completes instantaneously but returns control to an immediately enclosing trap... end which introduces a trap scope. The third completion level exit 1, abbreviated pause, does not terminate but completes by *pausing*. It waits for the next macro-step in which it will then terminate instantaneously. These exit statements are well known from Esterel [6].

Sequential composition  $P_1$ ;  $P_2$  first executes  $P_1$  until it terminates and then continues with  $P_2$ . When  $P_1$  exits or pauses, then also  $P_1$ ;  $P_2$  exits or pauses, respectively. The prescriptive program order between  $P_1$  and  $P_2$  implements a *sequentially constructive* semantics differing from traditional synchronous languages such as Esterel. In Esterel, the semicolon acts like a parallel composition with an extra control wire that permits  $P_2$  to start only when  $P_1$  has terminated. Since the statement blocks  $P_1$  and  $P_2$  are parallel, there may be a causality cycle between them in Esterel. In SCPL, the program  $P_1$ ;  $P_2$  can never have a causality cycle unless this it already exists in  $P_1$  or  $P_2$ .

In the parallel composition  $P_1 \parallel P_2$ , both processes  $P_1$  and  $P_2$  are executed to completion, concurrently in separate threads. Their statements are interleaved according to the policy interfaces associated with method and procedure calls as described below. The completion level of the parallel  $P_1 \parallel P_2$  is the maximum of the completion levels of both threads. Specifically, the parallel terminates (k = 0) when both threads  $P_1$  terminate. It exits (k = 2)if one of the threads exits, though letting the other thread run to completion. Otherwise, in an instant where one of the threads pauses (k = 1) and the other does not exit (k = 2), the parallel construct also pauses. Again, both threads run to completion. This behavior coincides with the standard semantics of synchronous parallel AND from languages such as Esterel (for general completions  $k \in \mathbb{N}$ ) or SCCharts (for completions  $k \leq 1$ ). The construct if e then  $P_1 else P_2$  expresses conditional branching of control flow. First, the condition e is evaluated and then, depending on its value, either  $P_1$  or  $P_2$  is instantaneously executed. In particular  $P_1$  and  $P_2$  may overwrite memory that was read by e because these writes take place sequentially after the condition test. Notice, we ensure that the conditional e is evaluated strictly before any of the branches  $P_1$  and  $P_2$  can start. Hence, the evaluation of e cannot depend on any statement inside  $P_1$  or  $P_2$ . This sequentially constructive semantics makes the conditional in Blech behave like in SCCharts rather than Esterel. Furthermore, the branches  $P_1$  and  $P_2$  are mutually exclusive, like in SCEst. In Esterel, for contrast, a conditional if e then  $P_1$  else  $P_2$  end can be equivalently coded as a parallel composition of one-sided conditionals if e then  $P_1$  end  $\parallel$  if e else  $P_2$  end. This can create causality cycles between  $P_1$  and  $P_2$  in Esterel, which do not exist in SCPL or SCEst.

The operator  $P_1 \not\models P_2$  is a parallel OR with built-in preemption sequentialised from left to right. We first run  $P_1$  to completion, disregarding any policy constraints between  $P_1$  and  $P_2$ . Once  $P_1$  completes, there are three possibilities depending on its completion code. If  $P_1$ terminates or exits, then  $P_2$  is instantaneously aborted and the construct terminates or exits, respectively. This is the *strong abort* behavior of the construct. If however  $P_1$  pauses in state  $P'_1$ , then control passes instantaneously to  $P_2$  which is permitted to complete the macro-step. When  $P_2$  terminates (exits), the configuration  $P'_1 \not\models P_2$  terminates (exits) as well, thereby *weakly aborting*  $P_1$ . If  $P_2$  pauses in state  $P'_2$  then the construct pauses in state  $P'_1 \not\models P'_2$ . This generates a cycle-wise, round-robin sequential left-to-right evaluation which cannot be expressed in Esterel. In SCCharts [8], which is sequentially constructive, the operator  $\not\models$  does not exist but can be coded. Céu [5] does implement this operator as par/or but it does not have any equivalent of  $\parallel$  nor a notion of causality.

The statement let x = o.m(e) in P calls a *method* m in a structure identified by *memory* path o. Methods are actions on the memory, defined outside SCPL and not to be confused with procedures. The value of expression e is the (composite) input argument of the method and the return value is bound to the value variable x. Sequentially after the atomic execution of o.m, which may have a side-effect on memory, control is passed to P, which may depend on the return value x. The value of x is not stored in memory. It is thread local and its scope is P. For example, an assignment x := y + 13 where x and y are memory references would be represented by the sequence let x = y.rd() in let  $_{-} = x.wr(x+13)$  in nothing. For convenience, we will abbreviate let x = o.m(e) in P as x := o.m(e); P when x is used in P and as o.m(e); P, otherwise.

Control flow loops are expressed as loop P. The thread P is run until it terminates, whereupon P is repeated, instantaneously, from the beginning. We can build terminating rules using loop and trap as we will see in the next section.

A procedure call  $\operatorname{run} p(\overline{o})$  instantiated from a static declaration  $\operatorname{proc} p(\overline{x}) = P$  starts the precompiled procedure body P, passing a list  $\overline{o}$  of memory paths by reference. The mapping  $f = [\overline{o}/\overline{x}]$  is subject to static typing and policy constraints as described below. The callee p may access the memory through method calls of the given arguments. The procedure is a generic control-flow process that is statically associated with the name p as an external host code or a precompiled SCPL process. The procedure is run atomically until it completes by either pausing or terminating. Procedures provide a general form of behavior abstraction in which arbitrary control flow (subject to interface restrictions) can be encapsulated. Concurrent instantiations  $\operatorname{run} p(\overline{o}_1) \parallel \operatorname{run} p(\overline{o}_2)$  will execute the same program code in concurrent threads. This is permitted provided the procedures do no create data races on the memory structures

| Assignment             | x = y  op  z                                        | $	extsf{let} v_1 = 	extsf{y.rd}() 	extsf{in}$<br>$	extsf{let} v_2 = 	extsf{z.rd}() 	extsf{in}$                   |

|------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                        |                                                     | let $\_=$ x.wr $(v_1 \text{ op } v_2)$ in nothing                                                                |

| Conditional statement  | if c then P else Q end                              | if $c$ then $P$ else $Q$                                                                                         |

| Loop                   | repeat P until c end                                | trap(loop(                                                                                                       |

|                        |                                                     | P; if $c$ then exit))                                                                                            |

| Sequential composition | PQ                                                  | P ; Q                                                                                                            |

| Reaction step          | await c                                             | repeat pause until c end                                                                                         |

| Preemption             | when c abort P end                                  | await c $ ight angle P$                                                                                          |

| Return from procedure  | return e                                            | rv = e; exit 2                                                                                                   |

| Activity declaration   | activity A $(\overline{\iota})(\overline{o})$ P end | $\operatorname{proc} A(\overline{\iota}, \overline{o}, \mathtt{rv}) = \mathtt{trap} \ \mathtt{P} \ \mathtt{end}$ |

| Activity call          | run A $(\overline{o}_1)(\overline{o}_2)$            | $\operatorname{run} A(\overline{\mathbf{o}}_1, \overline{\mathbf{o}}_2)$                                         |

| Cobegin                | cobegin P with Q end                                | $P \parallel Q$                                                                                                  |

| Cobegin with weak      | cobegin weak P with Q end                           | $(P \)$ await t) $\parallel (Q; t=true)$                                                                         |

Fig. 3. Rewrite rules that transform a Blech program into an SCPL program. The result is obtained by applying these rules recursively. A few remarks: In SCPL expressions are purely built on values. Therefore, assignment is decomposed into reading memory cells, combining the obtained valued and then writing the result back into memory. Analogously, we assume every Blech condition *expression* c is mapped to a boolean *value* c in SCPL by prepending a corresponding assignment. If the else branch is missing, nothing is used in the else-case of the SCPL program. SCPL only has an infinite loop. Therefore it is wrapped in a trap and a guarded exit 2 is added as the last statement to the loop's body. Conceptually, this construction separates control flow of the loop and the evaluation of the condition *inside* the loop. This makes the formal semantics simpler. In Blech a whitespace (or semicolon) token is used to separate statements whereas a semicolon must be used in SCPL. An SCPL procedure has only one parameter list which comprises all input and input-output parameters. A fresh variable rv is used as the designated procedure output to store the value of expression e to be returned. By means of a scheduling policy (Sec. VI) one can ensure that input parameters  $\bar{\tau}$  can only be read. Cobegin with strong branches is directly mapped onto  $\parallel$ . Using a fresh termination flag t we can encode a weak branch in SCPL. Symmetrically, the same construction works if the second branch is weak or both branches are weak.

shared between  $\overline{o}_1$  and  $\overline{o}_2$ . To this end, each procedure p has an associated causality interface  $\pi_p$ , called a *p*-policy, which specifies its synchronization with the memory. The interface  $\pi_p$  is instrumental not only to avoid races but also in order to guarantee memory safe, wait-free execution of each individual call. This will be explained in detail later.

## IV. MAPPING BLECH TO SCPL

SCPL is designed to be a compact formalism for studying semantics. It is not a practical programming language in any specific domain. In this section we argue that semantics of languages used in practice may be formally explained by mapping them to SCPL. This can be shown for Esterel, SCEst and in particular we consider Blech [18] here.

Blech<sup>1</sup> is an imperative, synchronous language that offers high-level abstractions and safety guarantees for reactive, real-time embedded programming. Blech compiles to C code, which may be integrated into existing projects or simulation frameworks. What makes Blech interesting for our purposes is that it is among the first ISP languages with first-class procedures that does not depend on white-box inlining. However, there is no formal semantics for it, yet. As indicated in Sec. II, a simple form of policy interfaces is already built into the language by design to support common programming patterns and guarantee an easy-to-understand behavior.

<sup>1</sup>blech-lang.org

The rules in Fig. 3 map Blech syntax to SCPL. We take the liberty to also map to a mix of SCPL with Blech when it is clear how to further transform the intermediate term to pure SCPL. Figure 3 only shows the essential control flow statements of Blech. More constructs are found in our example in Fig. 1: the return being the last statement in an activity can be understood as a one-time assignment to a special (anonymous) output parameter. Furthermore, a cobegin with more than two branches can be rewritten as a nested cobegin with only two branches at each level by grouping together strong and weak branches. Other constructs in Blech that are not shown in our example, too, may be rewritten inside the language itself: A while-loop can be rewritten as a repeat-loop. The Blech statement when c reset P end is a shorthand notation for an abort inside a loop that restarts P *if it was preempted*. Blech functions can be mapped to SCPL procedures in the same way as activities. Finally note, that Blech allows arbitrary expressions on the right hand side of assignments or as input arguments. They can be rewritten in static single assignment form and therefore our mapping assumes only variable names in procedure arguments and only a binary right hand side of an assignment.

The focus of this work is to explain the operational semantics of a program. Thus we do not consider Blech constructs that are only used for structuring a program such as do-blocks, variable declarations, namespaces and modules. We assume these have been resolved statically by the compiler.

### V. SYNCHRONOUS ACTIVITIES

The notion of activities is central to the design of Blech and the primitive notion of a schedulable unit of synchronous computation. The behavior of an activity lies in its (destructive, updating) side-effects on memory. By executing its side-effects in lock-step with a global clock, an activity implements a sequence of macro-step reactions that are synchronized with the reactions of other running activites. In each reaction step input data (stimulus) is read from memory and output data (response) is written back. An activity in Blech can have multiple input parameters and output parameters of different types through which it can communicate with its calling thread. The input value is taken when the activity is started and the output value returned when it completes. Here, for simplicity, we assume each activity takes a single start value and returns a single output value, both taken from a fixed global domain  $\mathbb D$  of values. Since it is a black-box, once an activity is started it cannot be interrupted until is has run to completion. Different types of completion are used to pass control to different continuation activities through which these are chained up for sequential control flow. In this report, activites have three ways to complete: termination, pausing or return. In each case, upon completion, also a completion value is passed back to the calling thread which forms the output parameter of the activity.

# **Definition 1 (Synchronous Activity)** A synchronous activity p on stores S with (local) control states Q consists of

- an initialisation function  $p.init : \mathbb{D} \to Q$ ;

- a step function  $p.step : \mathbb{S} \times Q \to \mathbb{S} \times Q$ ;

- a completion predicate ↓<sub>p</sub> ⊆ Q × {0, 1, 2} × D written q ↓<sub>p</sub> (k, v) instead of (q, k, v) ∈ ↓<sub>p</sub> for q ∈ Q, v ∈ D, k ∈ {0, 1, 2};

- *a* tick operation  $p.tick: Q \rightarrow Q$ .

The relation  $\Downarrow_p$  is a partial function in the first argument, i.e., if  $q \Downarrow_p (k_1, v_1)$  and  $q \Downarrow_p (k_2, v_2)$ then  $k_1 = k_2$  and  $v_1 = v_2$ . A state  $q \in Q$  for which  $\Downarrow_p$  is undefined is called incomplete. The initialisation function  $p.init(v) = q_0 \in Q$  selects the start control state of the activity, depending on a *start value*  $v \in \mathbb{D}$ . The function p.init is called in the macro step in which the activity is executed for the first time. From then on, unless the activity is preempted, the step function  $p.step(\Sigma, q_n) = (\Sigma', q'_n)$  is used to execute a single synchronous reaction of pfrom a given store  $\Sigma \in \mathbb{S}$  and current control state  $q_n$ . The result of the reaction is to produce an updated store  $\Sigma'$  and a completion state  $q'_n$ . If we have  $q'_n \Downarrow (k, v)$ , the completion state provides the *completion value* v and the *completion code* k indicating *termination* (k = 0), *pausing* (k = 1) or *return* (k = 2). When k = 1 the activity is pausing, i.e., it synchronizes with the global clock of the environment. All concurrent activites run in lock step and thus must synchronize with each other on the clock tick when pausing.

Note that it does not matter whether or not the sequence of initialisation *init* and *step* operations (in the starting macro-step) and the sequence of *tick* and *step* (in each subsequent macro-step) are executed atomically for each running activity. This is because the effects of the *init* and *tick* operators are isolated from each other as they only change the local control state of the activites. Synchronous activites communicate with each other and with the environment only through the store. While an activity is pausing, the environment can safely update the store with new external data (e.g., from the user interface) to prepare for the next macro step. In line with the synchronous model of execution (Synchrony Hypothesis [1], [19], [20]), new input data are set only when all concurrent activites. When all activities have completed, each paused activity is advanced to the control state  $p.tick(q'_n) = q_{n+1}$  from which the *next macro-step* is obtained. Although the tick function is only used on paused states with  $q'_n \Downarrow (1, v)$ , it is convenient to assume that it acts as the identity on all other states, making *tick* a total function on Q.

Note that the function  $\Downarrow$  is partial. It may not assign a completion code and value to every given control state. The control states for which completion is typically not defined are the initial states  $p.init(v) \in Q$ . These states still contain unevaluated program expressions which only stabilise by executing the step function. For most purposes, we may assume that the initial states are the only incomplete states. Specifically, every macro step of a precompiled black-box activity (external procedure, external method call) must complete and yield a stable state. The structural semantics of white-box scheduling, as introduced later, will give a more concrete motivation for incomplete states. For now it suffices to imagine the complete states, i.e., the control states in the domain of  $\Downarrow$ , as being analogous to the normal forms in  $\lambda$ -calculus and the step function p.step as being analogous to a  $\beta$ -reduction normalisation procedure. With the convention that we always apply the step function on the initial state before we extract the completion value, we may assume that all control states are complete (simply chose a random completion code and value in initial states). In this vein, henceforth  $\Downarrow$  is considered a total function.

The notion of a synchronous activity as per Def. 1 is meant to capture the black-box semantics of arbitrary syntactic fragements of a (sequentially constructive) synchonous programming language like Blech [18], SCCharts [8] or SCEst [21]. The term 'activity' has been introduced by Blech where the idea of a step function as a procedural side-effect on a global store has been identified more prominently than in earlier (more academic) synchronous languages. To be precise, Blech distinguishes between *activities* and *functions* which are two slightly more specific forms of synchronous activities, as we define them here.

- A Blech activity is a synchronous activity p with a unique initial state and that always either terminates or pauses on completion, but cannot return. Formally,  $p.init(v_1) = p.init(v_2)$  for all  $v_1, v_2 \in \mathbb{D}$  and if  $q \Downarrow_p (k, v)$  then  $k \neq 2$ . A Blech activity also gives informative completion values only upon termination not on pausing. This can be captured by saying that the completion value is constant on pausing states, i.e., if  $q_1 \Downarrow_p (1, v_1)$  and  $q_2 \Downarrow_p (1, v_2)$  then  $v_1 = v_2$ .

- A Blech function executes some side-effect on the store and instantaneously returns with a value. A Blech function thus is the special case of a Blech activity p for which the step function always terminates, i.e., q ↓<sub>p</sub> (0, v) for all q ∈ Q. Since the step function is only executed once on the initial state which itself does not depend on the start value, we may assume that the set of control states is the set of values, e.g., Q = D and v ↓<sub>p</sub> (0, v).

Both activities and functions in Blech communicate through side-effects in the memory. At the same time they can pass completion values into the calling threads and thus influence their control-flow. If we only permit pausing (k = 1) and remove the completion values altogether (assuming they are constant and thus redundant) we have the standard *synchronous Mealy machine* model with stores S as the input and output domain. For contrast, a *pure function* is a Blech function (see above) with  $Q = \mathbb{D}$  and for which the step function is constant, i.e.,  $f.step(\Sigma, q) = (\Sigma, q)$ . In this case, the function behavior lies in entirely in the initialisation  $f.init : \mathbb{D} \to \mathbb{D}$ . Pure functions cannot communicate through memory but must pass values explicitly and sequentially in the calling thread which calls one function and then passes the completion value as argument to another function. In this way, the semantics of synchronous activities includes the classical pure functional model of  $\lambda$ -calculus.

In our kernel language SCPL we use two other special forms of synchronous activities, called *procedures* and *methods*. These still capture the essence of Blech activities and Blech functions, yet permit somewhat simpler operator syntax.

- An SCPL procedure is a synchronous activity that can terminate or pause and does not have start or completion values. In other words, a procedure is a Blech activity without completion values, or equivalently a synchronous Mealy machine with termination. A procedure declaration proc p[x<sub>1</sub>, x<sub>2</sub>, ..., x<sub>n</sub>] = P defines a global activity p operating in a generic memory context that is introduced by the formal path parameters x<sub>1</sub>, x<sub>2</sub>, ..., x<sub>n</sub>. It can be instantiated in procedure calls run p[o<sub>1</sub>, o<sub>2</sub>, ..., o<sub>n</sub>] for different actual memory paths o<sub>1</sub>, o<sub>2</sub>, ..., o<sub>n</sub>. Since procedures are global, their names are absolute and not qualified by memory paths.

- An SCPL method m is similar to a Blech function<sup>2</sup>, i.e., a synchronous activity for which the step function always terminates. We sometimes call such synchronous activities *instantaneous*, because they return to the calling thread in the same macro-step (tick) in which they are called. In contrast to a Blech function which is also instantaneous, an SCPL method is treated as primitive while Blech functions are declared generically like procedures. Typical examples of methods in our sense are the implicit read and write accesses to memory variables in the expressions and assignments of the source-level syntax. These are not user-defined but built-in by the run-time system. In the syntax of the source level language, methods might also be declared as complex access methods along with abstract data types. An important point to note is that method calls operate

$^{2}$ We use the term 'method' in analogy with the methods in object-based programming. This stresses the side-effect on the store and prevents any confusion with pure functions that are side-effect free.

in statically fixed memory locations. This is the reason why we are able to resolve all memory aliasing and scheduling causality between procedure calls in our semantics.

We are now going to introduce our semantics of memory accesses bottom up. We start with the built-in semantics for method calls in the following Sec. VI. Procedures are declared as processes that execute individual method calls in sequential and concurrent control-flow. Their semantics will be induced by the semantics of methods calls via the structural operation semantics discussed in Sec. VII.

## VI. THE SCPL MEMORY MODEL

A SCPL program is executed in a store structured into a system of memory contexts. These constitute a name space to access and manipulate the data stored in the memory cells of the store. A *context* is a set of typed memory *paths* O. For each  $o: t \in O$  a set Mtd[t] of context *methods* is determined by the *path type t*, which is assumed to be statically fixed. Each path has exactly one type, i.e., if  $o: t_1 \in O$  and  $o: t_2 \in O$  then  $t_1 = t_2$ . The memory paths are the entry points into the shared data store, providing a primitive notion of locality and separation. The set of *qualified methods* (*qmethods*) available in a memory context is  $Mtd[O] = \{o.m \mid o: t \in O, m \in Mtd(t)\}$ .

**Example 1** The memory paths  $O = \{n: int, b: bool, p: point3D, ...\}$  may be typed references to scalar memory cells such as integers, booleans or composite data structures such as point objects. The access methods on scalar memory will typically be

$$Mtd[int] = \{rd:unit \rightarrow int, wr:int \rightarrow unit\}$$

for reading and for writing and

$$\texttt{translate}_x:\texttt{float} \rightarrow \texttt{unit} \in Mtd[\texttt{point3D}]$$

for translating the point object in x-direction. Substructures of composite data can be modelled either through memory paths or via methods. For instance, take a method call p.x.wr(v)for writing the x coordinate of p. We may consider  $p.x:float32 \in O$  as a path and  $wr:float32 \rightarrow unit \in Mtd[float32]$  as the method. Alternatively, we can take  $p:point3D \in O$  as the path and  $x.wr:float32 \rightarrow unit \in Mtd[point3D]$  as the method.

**Example 2** The memory paths used by MacOp (see Fig. 1) at its declaration-site, are

$$O_{\text{MacOp}} = \{ms: \text{State}, a: \text{float64}\}$$

where a is a scalar memory cell of type float64 and ms a composite data structure of type State. The access methods for the scalar a are

$$Mtd[\texttt{float64}] = \{\texttt{rd}:\texttt{unit} \rightarrow \texttt{float64}, \texttt{wr}:\texttt{float64} \rightarrow \texttt{unit}\}$$

for reading and for writing a double precision floating point number. The members of the composite structure ms: State can be modelled through methods or via memory paths. In context  $O_{MacOp}$  a method call ms.m1.rd() is composed of path ms: State  $\in O_{MacOp}$  and method m1.rd: unit $\rightarrow$ float64  $\in Mtd[State]$ . Alternatively, in context

$$O'_{\text{MacOp}} = \{ms.m1, ms.m2, ms.acc, a\}$$

the path is ms.m1 and rd:unit $\rightarrow$ float64  $\in$  Mtd[float64] is the method. In both cases, we get the same set of quethods, i.e.,  $Mtd[O_{MacOp}] = Mtd[O'_{MacOp}] = \{ms.m_1.m_2 \mid m_1 \in \{m1, m2, acc\} \land m_2 \in \{rd, wr\}\}$ . Furthermore, we may also have a special method

$mac: float64 \rightarrow float64 \rightarrow float64 \rightarrow unit \in Mtd[State]$

for computing the MAC operation, taking as inputs the substructures of State determined by their fixed order.

Memory paths can reference standard simple data structure like signals, variables, buffers or composite structures like vectors or arrays. It may also encapsulate complex behaviors such as priority queues, external input-output devices such as displays or precompiled reactive modules.

**Example 3** In the Cronos modular compiler [9] an Esterel module  $m : module \in O$  is compiled as an ADA package where Mtd[module] contains accessor methods x.set:unit $\rightarrow$ unit to set each input signal x, methods y.rd:unit $\rightarrow$ bool to read each output signal y, partial step evaluation functions i.eval:unit $\rightarrow$ unit for modular scheduling and methods init, reset, run, clear all of type unit $\rightarrow$ unit for executing the module as a whole.

For most of this report, it suffices to consider a factorisation of memory actions through "triple qualifications" o.m(v) consisting of memory paths o :  $t \in O$ , context methods  $m \in$ Mtd[t] and start values  $v \in \mathbb{D}$ . In general, a memory context will appear as a tree-like name space with overlap, i.e., some memory paths may be aliases of other paths of the same type. The tree structure is represented in Mtd[O] by iterated qualifications  $o_1.o_2....o_n$  generated by nested struct types. To allow for potential memory aliasing, the memory context comes equipped with a binary sharing relation # of qmethods Mtd[O]. The condition  $o_1.m_1 \# o_2.m_2$ states that the qmethods  $o_1.m_1$  and  $o_2.m_2$  have overlapping memory locations. This indicates that their side effects potentially conflict with each other, and thus their relative order of execution must be kept observable to maintain determinate program behavior. The dual is the relation  $\diamond$  of *insulation*, so that  $o_1.m_1 \diamond o_2.m_2$  means the two methods operate in separated memory locations and can be executed in any (uncontrollable, unobservable) order. In our notion of precedence policy defined below (Def. 4) we will refine these relations in terms of a *precedence* relation  $o_1.m \rightarrow o_2.m_2$ . We will not consider how the static structure on Mtd[O] is introduced through the typing of data structures and possibly aliasing arising from memory references. As mentioned before, we assume this has been resolved by the compiler in the upstream static program analysis. Like the procedures, the methods Mtd[O] of a store are provided by the compiler and implemented externally as black-box synchronous activites.

The following definition of an *execution structure* (Def. 2) gives a compact algebraic reformulation of the semantics of method calls as synchronous activities (Def. 1). Furthermore, it adds the necessary structure to reflect the dependency of methods on memory path contexts.

**Definition 2 (Execution Structure)** An (execution) structure  $S = (\mathbb{S}, \bullet, \odot)$  is a domain  $\mathbb{S}$  of memory configurations, called (typed) stores together with memory actions  $\bullet$  and  $\odot$ . Each  $\Sigma : O \in \mathbb{S}$  has an associated path context O defining the methods applicable to the store  $\Sigma$ : For each  $o.m \in Mtd[O]$  the operation  $\Sigma \bullet o.m(v) \in \mathbb{D}$  yields the return value of o.m when called with parameter value  $v \in \mathbb{D}$  and  $\Sigma \odot o.m(v) : O \in \mathbb{S}$  is the updated store in the same context.

The operators • and  $\odot$  encapsulate the step function of the instantaneous synchronous activity o.m. Method calls have trivial control states  $Q = \mathbb{D}$  for coding the start and completion

values. The initialisation function introduces the method call's start value v into the control state, o.m.init(v) = v. From this initial state, the step function operates as  $o.m.step(\Sigma, v) = (\Sigma', v')$  such that  $\Sigma' = \Sigma \odot o.m(v)$  and  $v' = \Sigma \bullet o.m(v)$ . The new control state is terminated,  $v' \downarrow_{o.m} (0, v')$  exposing the completion value v' to the calling thread. The tick function for as method call is redundant and never executed. E.g., we may stipulate o.m.tick(v) = v.

The domain of stores needs to be uniform in the sense that the semantics of a method o.m for  $o: t \in O$  only depends on the type t not on the path name o. It must be invariant under type-preserving renamings of memory paths, called *path maps*.

#### **Definition 3 (Path Map and Uniformity)**

- A function  $f : O_1 \to O_2$  is a path map if  $f(o_1 : t_1) = o_2 : t_2$  implies  $t_1 = t_2$ . We extend path maps f to quethods and method calls by putting f(o.m) = f(o).m and f(o.m(v)) = f(o).m(v).

- The execution structure (S, •, ⊙) is (path) uniform if for every Σ<sub>2</sub>: O<sub>2</sub> ∈ S there exists a store Σ<sub>2</sub>[f]: O<sub>1</sub> ∈ S with

- $\Sigma_2[f] \bullet a(v) = \Sigma_2 \bullet f(a)(v)$  and -  $\Sigma_2[f] \odot a(v) = (\Sigma_2 \odot f(a)(v))[f]$ for every  $a \in Mtd(O_1)$ .

A uniform structure permits us to retract a store  $\Sigma_2$  over  $O_2$  along a path map  $f: O_1 \to O_2$ to a store  $\Sigma_2[f]$  which emulates o.m(v) in  $O_1$  by indirection via f, executing the renamed call f(o).m(v) in  $O_2$ . If P is a SCPL process in context  $O_1$ , i.e., all methods calls in P are from Mtd[O], then we will write P[f] for the process P in which all methods calls have been renamed by f. The *relocated* process P[f] is then executing in stores for context  $O_2$ .

**Example 4** Consider the path context  $O = \{x, y, z\}$  and processes

$$P = y.wr(8); x.wr(5); u:=y.rd(); (A||B)$$

$$A = if u = 5 then y.wr(0)$$

$$B = z.wr(2).$$

Let  $\Sigma$ : *O* be a store which implements x, y, z in disjoint memory cells. Then, the value that *P* reads from y is u = 8, whence the write to y in *A* is by-passed and *P* only writes to z in *B*. Consider the relocated process

$$P[f] = \mathbf{x}.\mathbf{wr}(8); \mathbf{x}.\mathbf{wr}(5); u := \mathbf{x}.\mathbf{rd}(); ((\mathbf{if} \ u = 5 \mathbf{then} \ \mathbf{x}.\mathbf{wr}(0)) \| B)$$

with path map  $f = [x/x, x/y, z/z] : O \rightarrow O$  where y is substituted by x while x and z remain fixed. In functional notation this is f(x) = x = f(y), f(z) = z. Now the value read into variable u is 5 and thus x is overwritten by 0. The aliasing of cells x and y through f has changed the behavior of P. If the execution structure is uniform, then the behavior of P[f]in a store  $\Sigma$  can be simulated with P in an "aliasing store"  $\Sigma[f]$  in which all actions on path y are redirected to take place in x.

Aliasing relocations may not only change the semantics of a process, they may also introduce non-determinism. Observe that both processes P and P[f] are deterministic and do not show any data races, because the concurrent threads  $A \parallel B$  and  $A[f] \parallel B[f]$  do not share memory. For the path map  $f' = [x/x, x/y, x/z] : O \rightarrow O$ , however, the relocation P[f'] creates a write-write conflict, because now both thread A and B concurrently write to x. In synchronous programming, processes P and P[f] would be considered constructively schedulable, while the process P[f'] is rejected as being non-constructive.

**Example 5** In the memory context  $O'_{MacOp}$  for MacOp (Ex. 2) consider a procedure operating on state ms,

proc A(ms) = ms.m1.wr(1.1); ms.m2.wr(19.0); v := ms.acc.rd(); if v > CAP then exit 2

which fills fields m1, m2 with values 1.1, 19.0; then reads the acc field, and if this value v is above CAP it exits (return), otherwise it terminates. A procedure call run  $A(\mathbf{s})$  could be modelled by the path map  $f: O'_{\text{MacOp}} \to O'_{\text{Accumulate}}$  where

$$f = [s.acc/ms.m1, s.acc/ms.m2, s.acc/ms.acc]$$

relocates the formal state parameter ms into actual state s of the Accumulate context. In this instantiation, all cells of ms are identified with s.acc. With the help of the path map we can write the procedure call uniformly as run A[f]. If  $\Sigma : O'_{Accumulate}$  is a store that defines some start value for state s, then the behavior of the instantiated process A[f] can be simulated in a store  $\Sigma[f] : O'_{MacOp}$  in which all actions on paths ms.m1, ms.m2 and ms.acc are redirected to take place in memory cell s.acc, respectively. Specifically, the call ms.m1(1.1) writes to the same cell as ms.m2(19.0), namely s.acc, which is the same from which the read ms.acc.rd obtains the test value v.

The locality of methods  $m_1 \in Mtd[t_1]$  and  $m_2 \in Mtd[t_2]$  for non-overlapping memory paths  $o_1 : t_1 \in O$  and  $o_2 : t_2 \in O$  in the same path context O may be captured by the requirement on the execution structure S that a quethod  $o_1.m_1$  cannot depend on and does not influence the behavior of a quethod  $o_2.m_2$ . Where name spaces overlap, however, we must protect the memory from data races and impose some synchronization on method calls.

**Example 6** For instance, the writing n.wr(1) and reading b.rd() on distinct scalar memory cells n:int and b:bool are independent and can be executed without synchronization. The same applies to the writing p.x.wr(20) and p.y.wr(30) of distinct coordinates of a point p. However, the reading n.rd() and writing n.wr(1) of the same path n conflict in stores in which cell n has a value different from 1. In data-flow programming such data races are eliminated by prescribing a write-before-read precedence of method  $o_1.wr$  over  $o_2.rd$  if  $o_1$  and  $o_2$  are overlapping memory paths.

**Example 7** In the context  $O'_{MacOp}$  consider the process

B(ms) = u := ms.m1.rd(); ms.acc.wr(2.0u); run MacOp(ms, ms.acc)

which overwrites the accumulator cell ms.acc with the doubled value of ms.m1 and then calls MacOp to perfom a single multiply-accumulate on state ms. In the parallel composition A(ms)||B(ms) with A(ms) from Ex. 5 we now have shared accesses on ms. The data races are avoided by prescribing a write-before-read precedence for overlapping memory paths  $o_1, o_2 \in O'_{MacOp}$ . This means that A is first permitted to write ms.m1.wr(1.1) before B can read ms.m1.rd(). The subsequent write ms.m2.wr(19.0) in A and the write-back ms.acc.wr(2.0u) of B can go unsynchronized, assuming that ms.m1 and ms.acc are distinct cells. Finally, the reading of ms.acc.rd by A must wait until MacOp has finished writing its output ms.acc. Every store must be protected by a scheduling policy which implements a set of causal precedences on the memory accesses. The semantics of SCPL (Sec. VII) will execute the actions of a program in line with these precedences. Here we use a simple algebra of *causal precedence graphs* which express *state-less* zation protocols. These eliminate the data dependence from the notion of *policies* as defined in [14]. This simplification makes policy-conformant schedulability a property of the static program syntax. Although this seriously restricts the class of constructive programs from a theoretical point of view, it is a typical restriction adopted for practical synchronous programming languages.

**Definition 4 (P-policy)** A precedence policy (p-policy) over O is a subset  $\pi \subseteq Mtd[O]$  of admissible methods equipped with a binary precedence relation  $\longrightarrow \subseteq \pi \times \pi$ . We use the following special notation to specify p-policies:

- If  $a, b \in \pi$  and  $a \dashrightarrow b$ , we write  $\pi \Vdash a \dashrightarrow b$ .

- If  $\pi \Vdash a \dashrightarrow b$  or  $\pi \Vdash b \dashrightarrow a$ , we say a and b are in conflict, written  $\pi \Vdash a \# b$ .

- If  $a, b \in \pi$  are admissible, yet  $\pi \not\models a \dashrightarrow b$  and  $\pi \not\models b \dashrightarrow a$ , then a and b are called concurrently independent, written  $\pi \not\models a \diamond b$ .

A precedence  $\pi \Vdash a \dashrightarrow b$  enforces the scheduling constraint that if in some execution action a and b happen together, then b is scheduled strictly after a. If  $\pi \Vdash a \diamond b$  then a and b may be executed concurrently in any order. On the other hand, if  $\pi \Vdash a \# b$  then a and b must run sequentially in the same thread. More generally, the semantics of  $\pi \Vdash a \# b$  is that the run-time ordering between a and b is computed by the program itself, possibly causally depending on input data. In contrast,  $\pi \Vdash a \diamond b$  permits the order of execution to be decided by the compiler or the run-time scheduler, i.e., by computations that are unobservable and uncontrollable by the program.

**Example 8** Consider a context with two distinct scalar dataflow paths  $O = \{x, y : t\}$  with read and write methods  $Mtd[t] = \{rd, wr\}$ . The memory is specified by a p-policy var with full admissibility var = Mtd[O] but restricted scheduling order. To capture the "write-before-read" dataflow causality, var must contain the precedences var  $\Vdash$  o.wr  $\cdots$  o.rd for each  $o \in \{x, y\}$ . Since any two write accesses conflict with each other, there must also be the precedence var  $\Vdash$  o.wr  $\cdots$  o.wr for each  $o \in \{x, y\}$ . In other words,

These precedences can be used for deterministic scheduling. For instance, in the parallel composition  $x := 5 \parallel y := x$  the assignment x := 5 with its implicit x.wr access is executed before the assignment y := x which contains a read access x.rd on the same variable. Obviously, the causal precedence var  $\Vdash x.wr \dashrightarrow x.rd$  eliminates any write-read data races.

Write-write races are eliminated by the (symmetric) causal precedence var  $\Vdash$  0.wr  $\longrightarrow$  0.wr which forbids concurrent threads to write to the same path. Thus, a program like x := $5 \parallel x := 7$  becomes unschedulable, and thus is rejected as non-causal. Note, in line with sequential constructiveness [8] the precedence constraint only applies to concurrent accesses. If the accesses are already resolved in sequential program order, as in y := x; x := 5 or  $y := x \upharpoonright x := 5$ , then the read x.rd takes place before the write x.wr. Similarly, sequentially ordered writes as in x := 5; x := 7 or  $x := 5 \oiint x := 7$  are ok.

Finally, note that var does not contain precedences between accesses to x and y, because these are separated in memory and thus var  $\Vdash x.m_1 \diamond y.m_2$  for all methods  $m \in \{ rd, wr \}$ .

**Example 9** If composite memory structures  $o: t \in O$  (e.g. Quartz [2] signals) behave like synchronous registers, they support the four methods  $Mtd[t] = \{\text{pre}, wr, rd, nxt\}$  where o. pre extracts the value from the previous instant, o. nxt writes the value for the next instant, while o.rd and o.wr are the read and write access to the value computed in the current macro-step. In the high-level syntax of Blech, composite memory structures are instantiated by declarations [var | let] o: t = e, where is t a structure type and e an expression determining a composite (deep) initialisation value. A memory path o tagged with var is mutable and if tagged by let is immutable. In the latter case, the structure is protected so the write methods o.wr and o. nxt are not permitted. Hence  $Mtd[lett] = \{\text{pre}, rd\}$  if o is immutable and  $Mtd[vart] = \{\text{pre}, rd, wr, nxt\}$  if o is mutable. The associated p-policy reg has all Mtd[O] admissible, implements the "write-before-read" causality on the current value of the structure and eliminates write-write races. Formally, for all  $o_1, o_2 \in O$ , if  $o_1$  and  $o_2$  overlap,  $reg \Vdash o_1.wr \cdots o_2.wr$ ,  $reg \Vdash o_1.wr \cdots o_2.rd$   $reg \Vdash o_1.nxt \cdots o_2.nxt$ . The reading of the previous value is independent from any other access, i.e.,  $reg \Vdash o_1.pre \diamond o_2.m_2$  and also  $reg \Vdash o_1.m_1 \diamond o_2.m_2$  for all non-overlapping paths  $o_1$  and  $o_2$ .

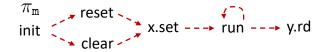

**Example 10** For a Cronos module m as described in Ex. 3 we build a p-policy  $\pi_m$  to express the internal coupling of methods as side-effects on the state, in order to protect the module from being used incoherently. Specified as a precedence graph, the p-policy looks as follows:

The initialisation init must be called before anything else. Then, clear or reset to reset inputs and registers can be made. In the third phase, the signal emissions x.set on inputs are scheduled, and only then the step function run can go ahead. When the step function is done, the output signals can be read with methods y.rd.

The precedence graph constrains concurrent accesses from producing memory glitches. E.g., note that the run method cannot be called concurrently, because it modifies the internal state in arbitrary ways. This is prohibited by the self-loop  $\pi_m \Vdash \text{run} \dashrightarrow$  run in the precedence relation. All other methods are without self-loops and can be called several times concurrently, because their effect is idempotent. This is specifically important for the setting of a signal x.set which may be called by several concurrent threads, in general.

The policy in Ex. 10 is an extended form of the *init-update-read* protocol (iur) of sequentially constructive (SC) variables introduced in [22] and used in SCCharts [8]. Specifically, an SC variable s (of any data type) supports the method s.ini of initialisation (called "absolute" writes), update s.upd (called "relative" writes) and reading s.rd. The associated init-updateread p-policy iur has the precedences such that

Hence, initialisations ini can only be performed by a single thread, updates upd must wait for initialisation but can be concurrent, and finally reads rd, too, can be concurrent but must wait for both ini and upd. The iur scheduling regime is itself a special case of a *scheduling directive* [23] which in turn is a special state-less case of a general policy [14].

The purpose of a p-policy is to ensure that all conformant schedules generate a deterministic response on the store in all macro-steps. For this to be true, the store must be *coherent* for the p-policy. The store together with the p-policy make up a *memory interface*.

**Definition 5** (Memory Interface & Coherence) A pair  $C = (O, \pi)$  consisting of a context O and a p-policy  $\pi$  is called a (memory) interface. A store  $\Sigma : O \in \mathbb{S}$  is C-coherent if all method calls concurrently independent under  $\pi$  commute with each other. Formally, let  $a, b \in Mtd[O]$  with  $\pi \Vdash a \diamond b$ . Then, for all  $u, v \in \mathbb{D}$ :

1)  $\Sigma \bullet a(u) = (\Sigma \odot b(v)) \bullet a(u)$

2)  $\Sigma \odot a(u) \odot b(v) = \Sigma \odot b(v) \odot a(u).$

Moreover, for all  $a \in Mtd[O]$  and  $v \in \mathbb{D}$  the updated store  $\Sigma \odot a(u) : O \in S$  must remain *C*-coherent.

Def. 5 is an extension of [14]. Condition (1) guarantees that the value returned by a method call a(u) does not depend on whether it is executed before or after a concurrently independent call b(v). Condition (2) expresses that final store does not depend on the order in which both calls are conducted.

**Example 11** The standard implementation of atomic read and write on a memory cell is coherent for the p-policy var. To implement reg coherently we need three memory cells, viz. to store the previous, current and the next value. This is expensive yet permits many causal programs. A tighter p-policy sreg could add extra precedences sreg  $\Vdash o_1$ . pre  $\dashrightarrow o_2$ .wr, sreg  $\Vdash o_1.wr \dashrightarrow o_2$ .nxt and sreg  $\Vdash o_1.rd \dashrightarrow o_2$ .nxt for overlapping  $o_1$ ,  $o_2$ . This interface can be implemented coherently with a single memory cell. However, the extended policy sreg is less concurrent and may leave some programs non-constructive. If a program, written under the reg memory interface, turns out to be constructive for sreg, then the registers can be optimised and implemented under var, by identifying the method nxt with wr and pre with rd.

**Definition 6 (Interface Extension)** An extension  $f : C_1 \subseteq C_2$  of interfaces  $C_i = (O_i, \pi_i)$  is a path map  $f : O_1 \rightarrow O_2$  such that if  $a, b \in \pi_1$  then  $f(a), f(b) \in \pi_2$  and if  $\pi_2 \Vdash f(a) \dashrightarrow f(b)$ then  $\pi_1 \Vdash a \dashrightarrow b$ .

If the extension is an inclusion  $f: O_1 \subseteq O_2$  of paths, then we drop f and write  $C_1 \subseteq C_2$ , or simply  $\pi_1 \subseteq \pi_2$ . In this case  $\pi_1$  enforces a more restrictive scheduling on a subset of the quethods from  $\pi_2$ , without any renaming of paths.

**Example 12** The discrete p-policy top contains all method calls Mtd[O] without any  $\cdots$  edges. It is the maximum element, i.e.,  $\pi \sqsubseteq$  top for every  $\pi$ . The p-policy top permits unconstrained concurrent access to the store. The empty p-policy bot  $= \emptyset$  admits no actions and represents a locked store, disallowing any memory access. It is the minimum element satisfying bot  $\sqsubseteq \pi$  for all  $\pi$ . The indiscrete p-policy seq is the fully connected  $\cdots$  relation on Mtd[O]. It specifies a store that can only be accessed by a single thread. The set of p-policies  $\pi \sqsubseteq$  seq is isomorphic to the set of (fully connected) subsets of Mtd(C). We have bot  $\sqsubseteq$  var  $\sqsubseteq$  sreg and bot  $\sqsubseteq$  seq  $\sqsubseteq$  sreg  $\sqsubseteq$  reg  $\sqsubseteq$  top.

Procedures are abstractions of control flow to manipulate the store. They encapsulate program modules generic in their memory context which is abstracted through context parameters. An procedure is accessed through its name and instantiated to a concrete memory context like a module in Esterel or a node in Lustre. In contrast to Esterel or Lustre, however, the memory that can be shared through concurrent procedures can be of general type and is not restricted to signals, buffers or data flow variables. In order to achieve modularisation, we do not depend on the source code of an procedure to be available. For our evaluation semantics, an procedure is a black-box that is precompiled like a host procedure in Esterel. However, in contrast to Esterel, an procedure has an associated causality interface.

Each generic procedure p comes with a memory interface  $C_p = (O_p, \pi_p)$  in which  $\pi_p$  exports the admissible qmethods through which the memory is potentially accessed and how these are causally dependent on each other. Interface extensions (Def. 6) is the key mechanism to instantiate procedures (see below). As an interface, the p-policy  $\pi_p$  embodies an assumptionguarantee contract between the external use context and the internal behavior of the procedure. Outside at the call site, the causal type implies a coherence constraint on the store for the procedure to be safely instantiated. Inside of the procedure, the causal type constrains the scheduling of memory accesses by the encapsulated implementation code. For instance, if  $\pi_p \Vdash b \dashrightarrow c$ , then the implementation must guarantee that any concurrent call to  $c \in Mtd[O_p]$ happens after any concurrent call to  $b \in Mtd[O_p]$ . The store then does not need to be protected against any data races arising from the b and c types of actions. On the other hand, if  $\pi_p \Vdash b \diamond c$ , then there is no precedence information about how the procedure will execute the method calls. Because of the potential race situation, this amounts to the coherence assumption on the store that the order of execution of b and c does not matter. The store must protect the accesses in order to stay coherent, in which case the implementation is free to schedule the accesses in any way it wants.

**Example 13** Every activity in Blech is a SCPL procedure. Consider the activity add as seen in Fig. 4. It consists of two threads. The first thread waits on variable b and terminates as soon as it has a value greater than 10. The second thread concurrently reads b and variable a and writes the sum of their values into an output variable s. The parameters

```

activity add(a: int32, b: int32)(s: int32)

cobegin

await b > 10

with weak

repeat

s = a + b

await true

end

end

end

```

Fig. 4. An activity add in Blech syntax. The example is taken from [18].

in the Blech interface by default are var type memory paths, so the available methods are  $Mtd[O_{add}] = \{a.rd, a.wr, b.rd, b.wr, s.rd, s.wr\}$ . The split parameter lists of the Blech interface however indicate that a, b are read-only, while s is a mutable output. Hence the p-policy is  $\pi_{add} = \{a.rd, b.rd, s.wr \cdots s.wr, s.wr \cdots s.rd\} \sqsubseteq$  var which guarantees that the add is not writing a or b at all, possibly writing s, but never concurrently, and also writes s before any concurrent reading of a. A tighter p-policy, exposing the fact that add is not reading s at all, and only writing it in the same thread in which it reads a is  $\pi_{add}^* = \{b.rd, a.rd \cdots s.wr, s.wr \cdots s.wr, s.wr \cdots a.rd\} \sqsubseteq \pi_{add}$ . Also, note that  $\pi_{add}$  and thus  $\pi_{add}^*$  are extensions of each of the var p-policies for variables a, b, and s individually.

**Example 14** Reconsider the activity Accumulate from Fig. 4. It consists of three threads. The first thread adapts the inputs from arr to the factors m1 and m2 of ms. The third thread waits on path ms.acc and terminates its value is greater than CAP. The second thread concurrently reads b and variable a and writes the sum of their values into an output variable s. The parameters in the Blech interface by default are var type memory paths, so the available methods are  $Mtd[O_{add}] = \{a.rd, a.wr, b.rd, b.wr, s.rd, s.wr\}$ . The split parameter lists of the Blech interface however indicate that a, b are read-only, while s is a mutable output. Hence the p-policy is  $\pi_{add} = \{a.rd, b.rd, s.wr \cdots s.wr, s.wr \cdots s.rd\} \sqsubseteq$  var which guarantees that the add is not writing a or b at all, possibly writing s, but never concurrently, and also writes s before any concurrent reading of a. A tighter p-policy, exposing the fact that add is not reading s at all, and only writing it in the same thread in which it reads a is  $\pi_{add}^* = \{b.rd, a.rd \cdots s.wr, s.wr \cdots s.wr, s.wr \cdots a.rd\} \sqsubseteq \pi_{add}$ . Also, note that  $\pi_{add}$  and thus  $\pi_{add}^*$  are extensions of each of the var p-policies for variables a, b, and s individually.

A procedure call run p[f] takes a procedure p with interface  $C_p$  and an interface extension  $f : C_p \subseteq C$  to evaluate its (precompiled) behavior in store  $\Sigma[f]$  for declaration context  $C_p$  for a store  $\Sigma$  of the call context C. The conditions of Def. 6 make sure that the procedure call is memory safe, even if the renaming f aliases memory paths.

**Example 15** Consider contexts  $O_{Accumulate}$  and  $O_{MacOp}$  from Fig. 1 such that

$$O_{\text{Accumulate}} = \{ arr: [2] \text{float64}, s: \text{State} \}$$

$O_{\text{MacOp}} = \{ ms: \text{State}, a: \text{float64} \}$

with admissible methods

$\begin{aligned} Mtd[[2]\texttt{float64}] &= \{[0].\texttt{rd}, [0].\texttt{wr}, [0].\texttt{rd}, [1].\texttt{wr}\} \\ Mtd[\texttt{State}] &= \{m\texttt{1.rd}, m\texttt{1.wr}, m\texttt{2.rd}, m\texttt{2.wr}, \texttt{acc.rd}, \texttt{acc.wr}\} \\ Mtd[\texttt{float64}] &= \{\texttt{rd}, \texttt{wr}\}. \end{aligned}$

The split parameter lists of Accumulate(arr: [2]float64)(s: State) indicate that arr is readonly, while s is mutable. The p-policies implied by this procedure header are given by

$$\pi_{\text{Accumulate}} = \{ arr.[0].rd, arr.[1].rd, \\ s.m.wr \dashrightarrow s.m.wr, s.m.wr \dashrightarrow s.m.rd \mid m \in \{m1, m2, acc\} \} \\ \pi_{\text{MacOp}} = \{ ms.m.rd, a.wr \dashrightarrow a.wr, a.wr \dashrightarrow a.rd \mid m \in \{m1, m2, acc\} \}.$$

The definition of  $\pi_{MacOp}$  implements the interface for a procedure header MacOp(ms)(a) and ignores the shares annotation in the actual procedure declaration MacOp(ms)(a shares ms.acc) of Fig. 1 for the moment. Hence  $\pi_{MacOp}$  expresses the concurrent independence

$$\pi_{\texttt{MacOp}} \Vdash a.\texttt{wr} \diamond ms.acc.\texttt{rd}.$$

This turns invalid through the instantiation run MacOp(s)(s.acc) in Accumulate with the path map f = [s/ms, s.acc/a] which aliases the formal procedure parameters ms and a to point to overlapping memory cells f(ms) = s and f(a) = s.acc. Because of this, the path map f is not an extension from the interface  $C_{MacOp} = (O_{MacOp}, \pi_{MacOp})$  under which MacOp is declared and implemented into the interface  $C_{Accumulate} = (O_{Accumulate}, \pi_{Accumulate})$  under which the call is executed. In fact,  $f : C_{MacOp} \not\equiv C_{Accumulate}$  because  $\pi_{Accumulate} \vdash f(a.wr) \dashrightarrow f(ms.acc.rd)$ but  $\pi_{MacOp} \not\models a.wr \dashrightarrow ms.acc.rd$ , considering that f(a.wr) = s.acc.wr and f(ms.acc.rd) = s.acc.rd. The situation is resolved if we now take into account the sharing 'a shares ms.acc'. This enforces the missing precedence  $\pi_{MacOp} \Vdash a.wr \dashrightarrow ms.acc.rd$  in the procedure's interface. Thus, f becomes an interface extension, at the cost that MacOp must internally synchronize accesses to a and ms.acc.

**Example 16** The generic interface  $\pi_{add}$  of the procedure add of Ex. 13 captures the coherence assumptions on the store for generic formal parameters a, b and s. We do not know how they are related, since these will be determined only at the call site of add. In particular, the concurrent independence  $\pi_{add} \Vdash b.rd \diamond s.wr$  turns invalid if both parameters get aliased through the instantiation. For instance, suppose we instantiate add in a call iadd = run add(a, c)(c) where a and b are the same memory cell c. The corresponding renaming f = |a/a, c/b, c/s|is not a extension  $f: (O, \pi_{add}) \subseteq (O, var)$  from the interface under which add is declared and implemented (p-policy  $\pi_{add}$ ) into the interface under which the call is executed (p-policy var). This is because var  $\Vdash$  c.wr  $\dashrightarrow$  c.rd but  $\pi_{add} \not\Vdash$  s.wr  $\dashrightarrow$  b.rd, although f(s.wr) = c.wrand f(b.rd) = c.rd. This has practical consequences for modular compilation: If the code for add is pre-compiled, rather than inlined, the method call add(a, c)(c) is unsafe and must be rejected. The generic interface  $\pi_{add}$  of add(a, b)(s) does not constrain the order in the reading of b and the writing of s. This will not matter, provided the memory referred to by b and s are separated. However, when b and s are instantiated with memory that are overlapping, then the ordering matters. Then the call add(a, c)(c) may produce unpredictable results with externally precompiled scheduling. Suppose on the other hand, the concurrent body of add(a, c)(c) is inlined and we are scheduling the code as white-box in the use context. Then, the (in this case unique) schedule will be chosen that satisfies the "write-before-read" policy var on cells a and c.

There are three ways for an unsafe procedure call  $\operatorname{run} p[f]$  to become memory safe. First, as in standard synchronous languages, such as Esterel, the procedure is inlined as white-box. Second, the calling context changes to another store, which is coherent for a more relaxed p-policy. Third, the implementation of p is forced to avoid potential memory glitches with a more restrictive p-policy like adding a sharing constraint.

**Example 17** For the instantiation run add(a, c)(c) in Ex. 16 to remain conformant with var we would need an inter-path precedence  $s.wr \cdots b.rd$  for the body of add, i.e., make sure that the read of cell b is guaranteed to see the effect of writing s. The code above in Fig. 4 does not achieve that, obviously. For contrast, consider the modified code add1 in Fig. 5 which implements a similar (but not the exactly same) behavior as add in a single thread.

Fig. 5. Single-threaded Blech activity add1.

There are no concurrent accesses so that the procedure interface  $\pi_{add1}$  can expose the constraint  $\pi_{add1} \Vdash s.wr \dashrightarrow b.rd$ . In the Blech code of Fig. 5 this is expressed via the sharing constraint 's shares a, b' in the interface of add1. Now the instantiated activity iadd1 =

run add1(a, c)(c) has  $\pi_{iadd1} \Vdash s.wr \dashrightarrow s.rd$ . Hence, we have conformance of  $\pi_{iadd1}$  with the policy of cell s, despite the aliasing. And of course, the instantiation add1' is thread safe, for trivial reasons. The activity add1 exports sharing information in its formal causality interface. The bi-directional precedences in the generic interface expose the essential single-threaded nature of the implementation code. After the aliasing instantiation as a method call all read accesses are protected by the causality order.

#### VII. OPERATIONAL SEMANTICS FOR SCPL